▲ Click☆Star me to prevent losing contact

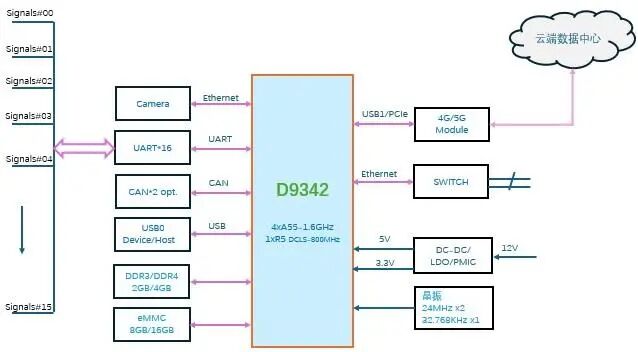

In the fields of power distribution automation and industrial automation, the communication management machine (DPU, Data Processing Unit) is an indispensable key device. It collects and organizes data from intelligent monitoring or protection devices through multiple downstream communication interfaces and one or more upstream network interfaces, and uploads it in real-time to the master station system or cloud data center, enabling remote measurement, data collection, and control functions.

Modern intelligent communication management machines integrate various cutting-edge technologies such as 4G/5G modules, edge computing, communication management, and protocol conversion, covering the “edge” and “end” of the smart IoT management system. They are an important component for achieving cloud-edge collaboration and edge-end interaction, widely used in smart grids, power IoT, and industrial interconnectivity.

Application scenario image

Core Technical Advantages

1. Efficient Interface Design

Equipped with up to 16 UART interfaces, it can connect measurement terminals directly without expansion or using FPGA, significantly reducing costs and saving board space.

2. Industrial-grade Durability

Supports a wide temperature range of -40℃ to 125℃, suitable for various harsh environments, truly achieving high reliability of industrial-grade SoC.

3. Precise Time Synchronization

Equipped with TSN (Time-Sensitive Networking) Ethernet functionality, supporting time-triggered message delivery and queue scheduling, ensuring low latency and high stability of data transmission, meeting the needs of time-critical applications.

4. Comprehensive Security Assurance

Supports international standard encryption algorithms (AES, RSA, DSA, etc.) and national secret algorithms (SM2, SM3, SM4, SM9), and has a secure boot function to ensure the security of data transmission and system operation.

5. Dual System Operation

Runs RTOS on Secure DCLS Cortex-R5 while running Linux on a 4-core Cortex-A55, meeting multi-task processing requirements.

Display board photo

Solution Specifications

Application CPU

– 4 ARM Cortex-A55 processor cores

– Each core includes 32KB I/D L1 Cache

– Each core includes 128KB L2 Cache

– 1MB L3 Cache

Security CPU

– ARM® Cortex-R5 processor, DCLS mode

– 32KB/32KB L1 I/D Cache

– 128KB L2 Cache

– Cache & TCM with ECC and parity functions

DRAM Interface

– 32-bit DRAM interface, 2400MT/s

– Supports DDR4/LPDDR4/LPDDR4x

– Supports In-line ECC

High-speed Interfaces

– 2 USB3.0 interfaces

– 2 PCIe3.0 interfaces, supporting RC/EP modes

– 2 Gigabit Ethernet interfaces, supporting TSN

HSM

– True random number generator

– High-performance Crypto algorithm engine

(AES, RSA, ECC, SHA, SM2/3/4/9)

Peripheral Interfaces

– 4 CAN-FD

– 8 SPI

– 16 UART

– 12 I2C

– PWM

– 12-bit SAR ADC

2GB/4GB LPDDR4X

8GB/16GB eMMC

Solution block diagram

Welcome to follow the DaLianDa Engineer Community – DaDaTong

👇👇👇

ClickRead the original text for more details!

Like

Collect

Share