Click the blue text to follow, grateful for your support

Click the blue text to follow, grateful for your support

Welcome to all friends to follow“Hao Xushuang Electronic Design Team“ public account, this public account will regularly update relevant technical materials, software, etc. Friends who are interested can browse other“modules“, hoping that all friends can gain something they want from this public account“things“.

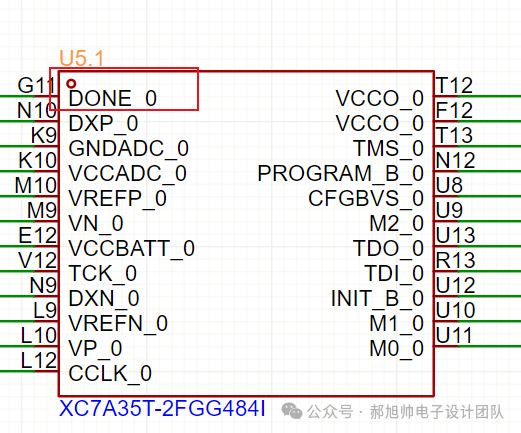

This article mainly discussesXilinx A7 FPGA’s DONE signal explanation

DONE signal is a key status indication signal output after the FPGA completes configuration and initialization. When the FPGA successfully loads configuration data (such as from external Flash or JTAG interface) and passes the verification, the DONE signal goes high, indicating that the FPGA is ready to enter normal operating mode.

The FPGA configuration process is divided into three stages: reset, configuration data loading, and initialization. The key points of the DONE signal in these stages are as follows:

Reset Stage

When the FPGA is powered on, if the nCONFIG pin is pulled low, the DONE signal remains low, and all I/O is in a high-impedance state.

Configuration Completion Stage

When the configuration data is fully loaded and passes the CRC check, the DONE signal changes from low to high-impedance state, and it needs to be pulled high by an external pull-up resistor, marking the end of the configuration stage.

Initialization Stage

After the DONE signal goes high, the FPGA begins to initialize internal logic and I/O registers, and upon completion, it enters user mode.

Pull-Up Resistor Value Selection

Typical value: Xilinx FPGA recommends using a 330Ω pull-up resistor (rather than the common 4.7kΩ) to avoid slow rising of the DONE signal, which could lead to initialization failure.

Failure case: If a 4.7kΩ resistor is used, at higher configuration clock frequencies, the DONE signal may fail to rise quickly enough, causing a GTS event (I/O enable) failure.

The equivalent signal for Altera FPGA is CONF_DONE, and its design principles are similar to those of Xilinx.

Some resources in this article are sourced from the internet; if there is any infringement, please contact the author.

If you think this public account is good, please recommend it to your friends, thank you and best wishes!