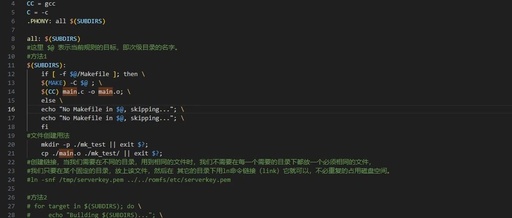

Linux Kernel Makefile Execution Process

Scan to FollowLearn Embedded Together, Learning and Growing Together Essential Knowledge 1.1. Basic Syntax of Makefile If you are not familiar with Makefile syntax, it is recommended to learn it systematically first, especially the following points: (1) Which parts of the Makefile contain shell commands: The command part in the compilation rules ${shell XX}, var … Read more