Scan to FollowLearn Embedded Together, Learning and Growing Together

Essential Knowledge

1.1. Basic Syntax of Makefile

If you are not familiar with Makefile syntax, it is recommended to learn it systematically first, especially the following points:

(1) Which parts of the Makefile contain shell commands:

The command part in the compilation rules ${shell XX}, var != XX in which XX is $(if …, XX, XX)

(2) Variable expansion: = (delayed assignment), := (immediate assignment), != (value as shell command), ?= (conditional assignment), += (append)

(3) include: Expands the content of specified other Makefiles into the current Makefile

-f/-C: Nested execution of specified (directory) Makefile

Executing a Makefile does not start from the first line but from the specified or default compilation target (the assignment statements before the position target compilation rules are executed only when the corresponding variable needs to be used), where the first target in the Makefile (including included content) is the default target. If no compilation target is specified on the make command line, the default target is executed.

(4) Automatic dependency file inference

(5) Judging dependency updates based on file timestamps and intermediate files (.d, .cmd) to decide whether recompilation is needed

(6) Important built-in functions:

$(wildcard pattern) $(patsubst pattern, replacement, text) $(strip string) $(filter pattern, text) $(filter-out pattern, text) $(call func, args..)…

(7) Automatically inferred variables:

$@: Compilation target $<: The first dependency object in the dependency list $^: All objects in the dependency list $? : All updated files in the dependency file list

For Makefile tutorials, you can refer to the following:

Write Makefile with me (Chen Hao): Make Command Tutorial | Step-by-Step Introduction to Makefile (Classic, Super Detailed)

1.2. Kbuild Built-in Functions

The Linux kernel source code includes a set of Makefile programs, this article analyzes based on the Linux-5.2.5 kernel source code, which includes the top Makefile, Makefile in the scripts/ directory, Makefile.build, Makefile.lib, Kbuild.include, Makefile.modpost, kconfig/Makefile, etc., as well as many sub-Makefiles in other directories, collectively referred to as Kbuild.

Kbuild is implemented according to the framework design concept, allowing a large number of driver modules included in the kernel or provided externally to compile by simply providing a simple Makefile according to the Kbuild framework conventions.

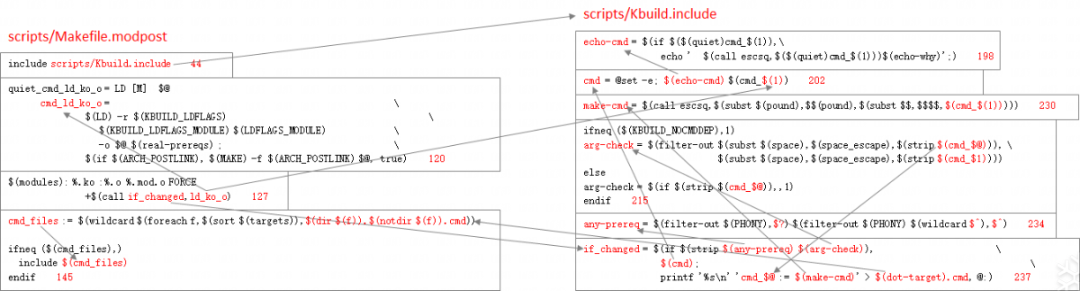

Therefore, understanding the compilation process of the kernel or driver files actually means understanding the implementation logic of this set of Makefile programs in Kbuild. Since it is a program, it inevitably defines some functions. Many key processes use $(build) and $(if_changed), so the following introduces them separately (the Makefile content analyzed in this article comes from the Linux-5.2.5 kernel source code):

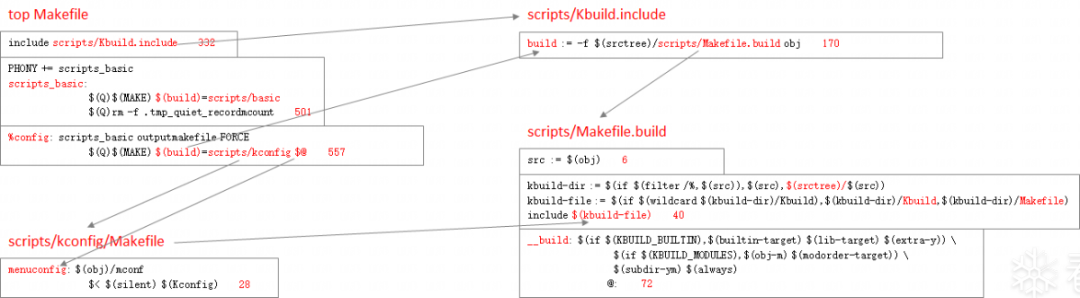

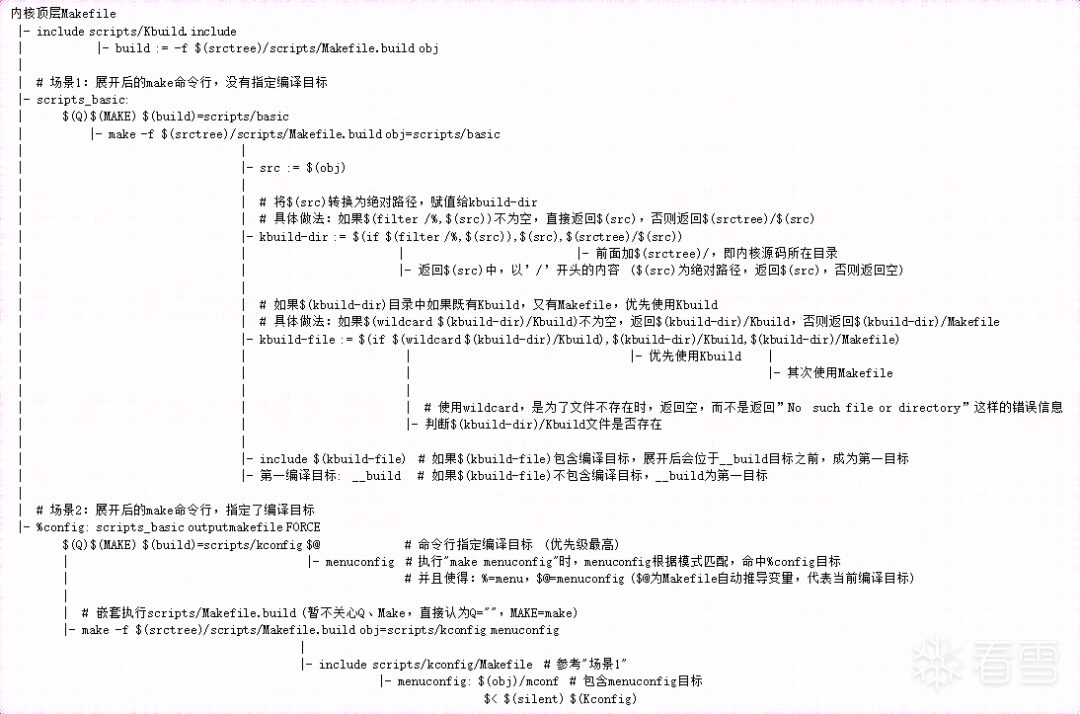

1.2.1. $(build)

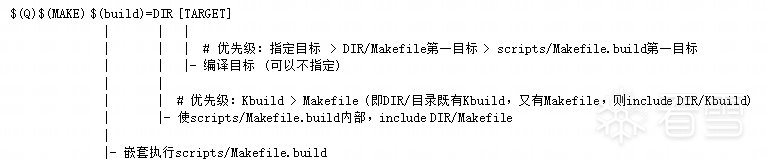

◆ Usage: $(Q)$(MAKE) $(build)=xx directory [compilation target]

◆ Internal process of build

◆ Summary of build function

Below is the usage form of $(build) and the role of each part:

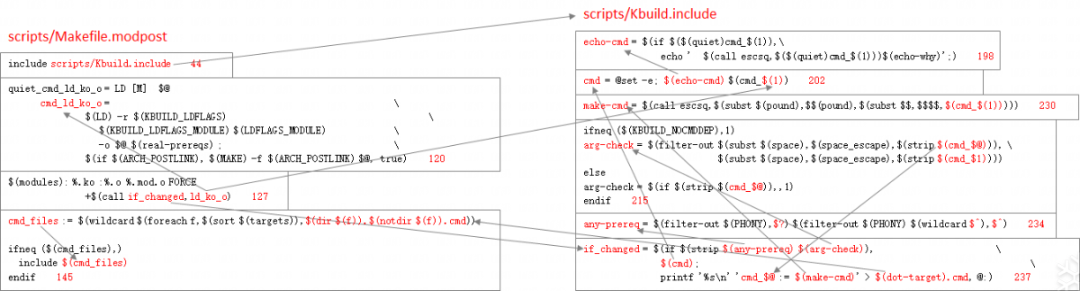

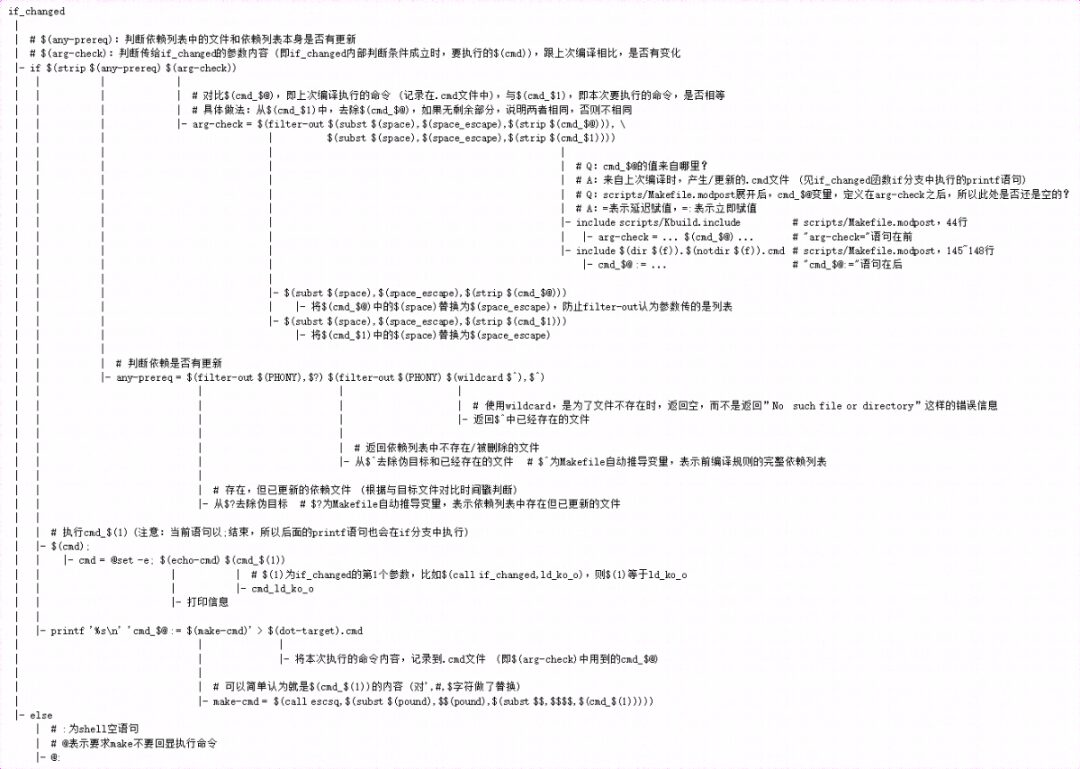

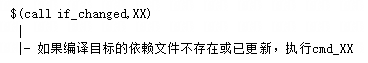

1.2.2. $(if_changed)

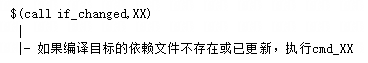

◆ Usage: $(call if_changed, xx) ◆ Internal process of if_changed

◆ Summary of if_changed function

Below is the usage form of $(if_changed) and the meaning of its parameters:

◆ Internal process of if_changed

◆ Summary of if_changed function

Below is the usage form of $(if_changed) and the meaning of its parameters:

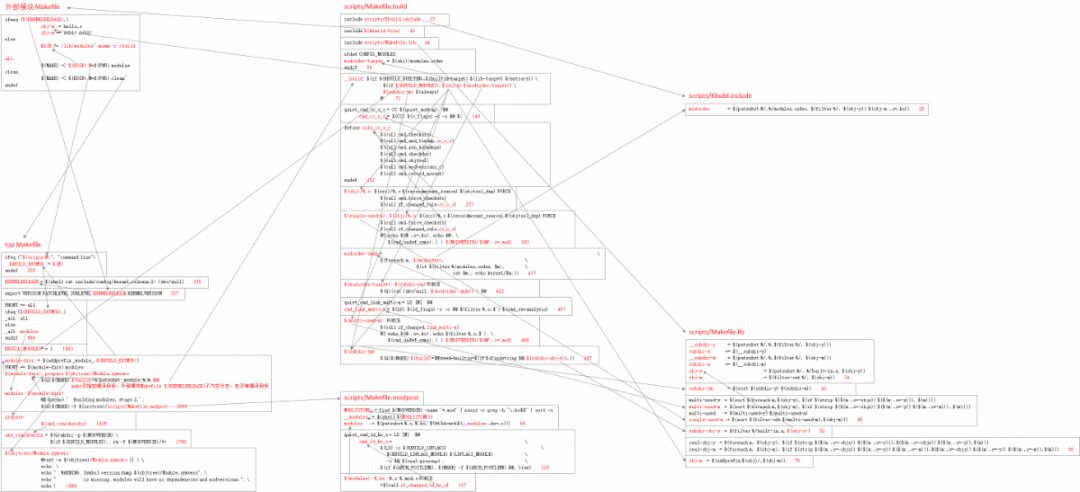

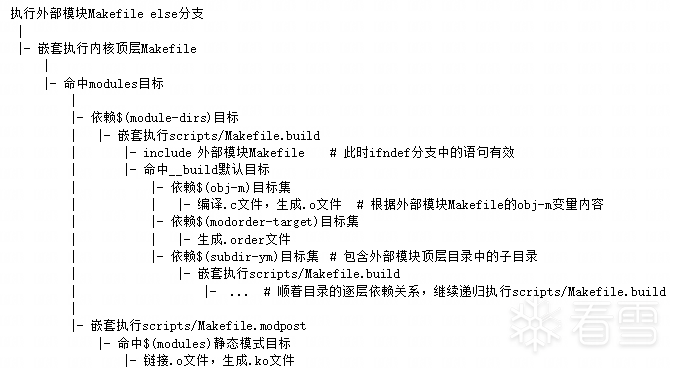

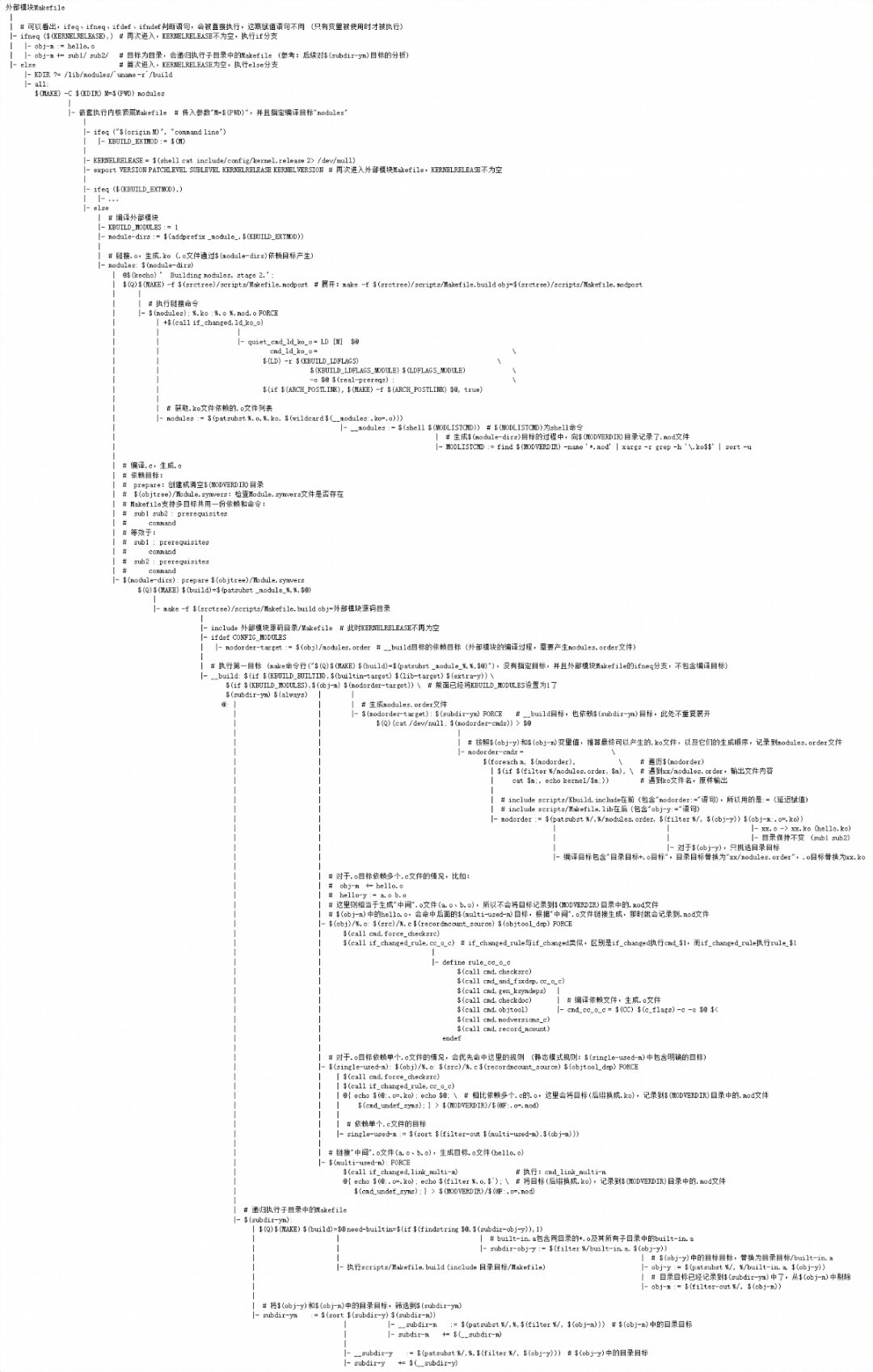

Compiling External Modules

2.1. Related Makefile Content

2.2. Summary Process

2.3. Detailed Process

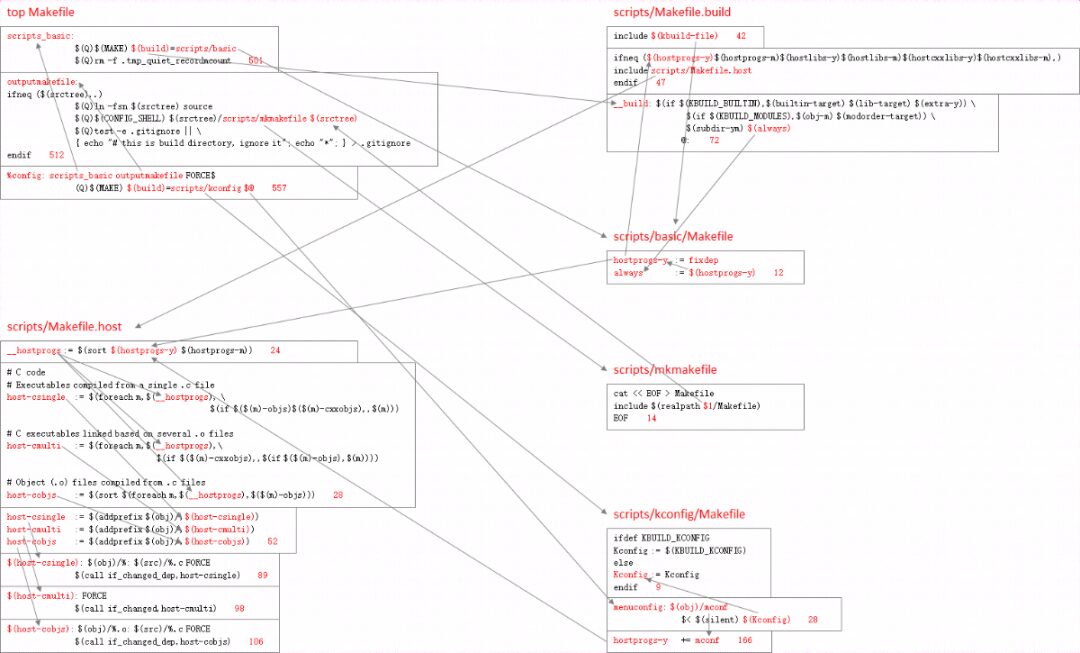

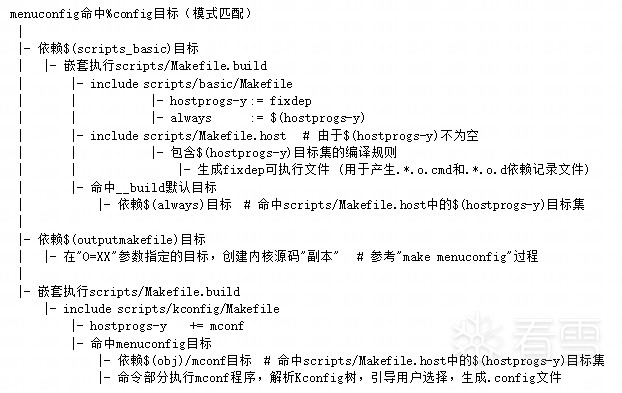

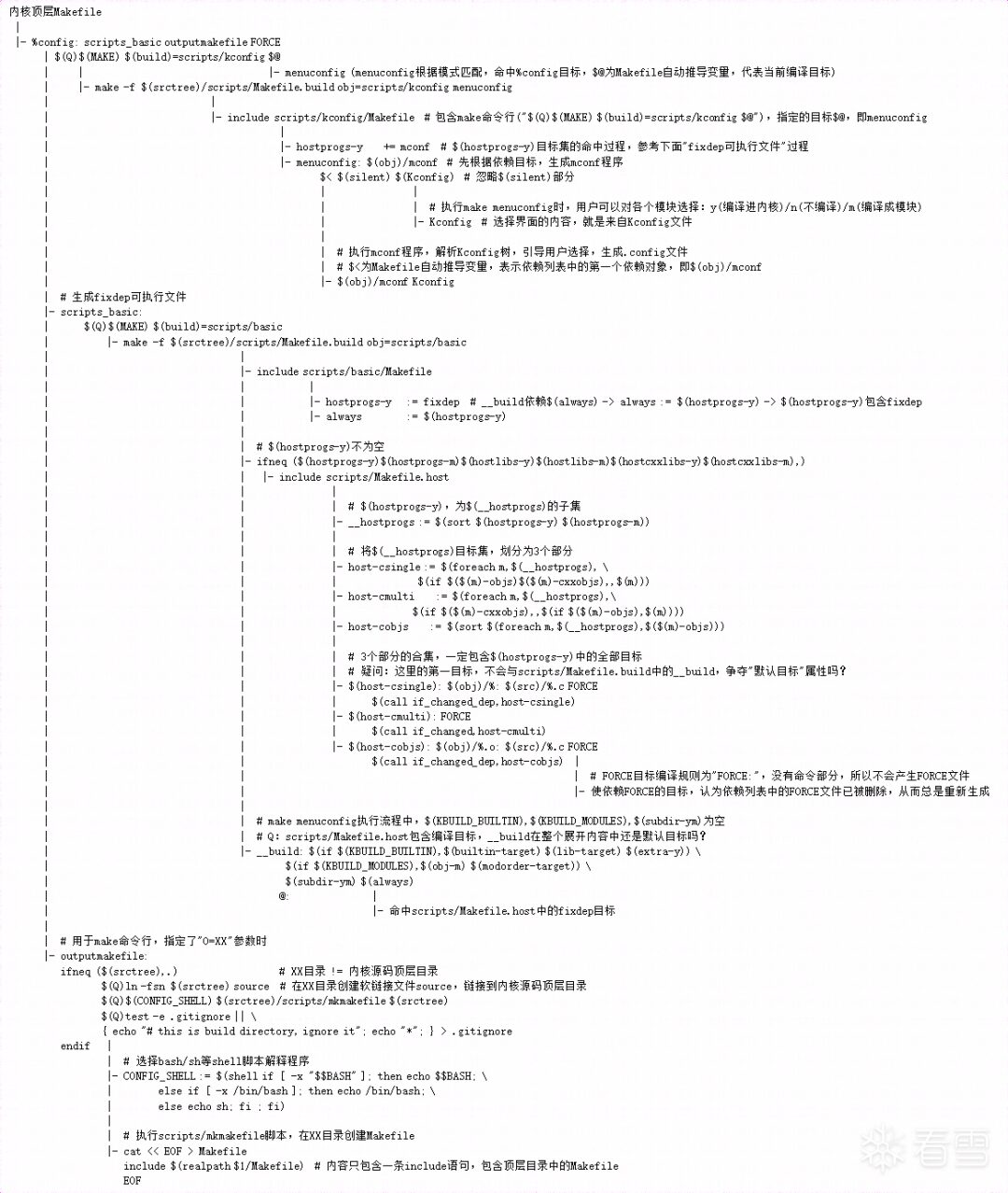

make menuconfig

3.1. Related Makefile Content

3.2. Summary Process

3.3. Detailed Process

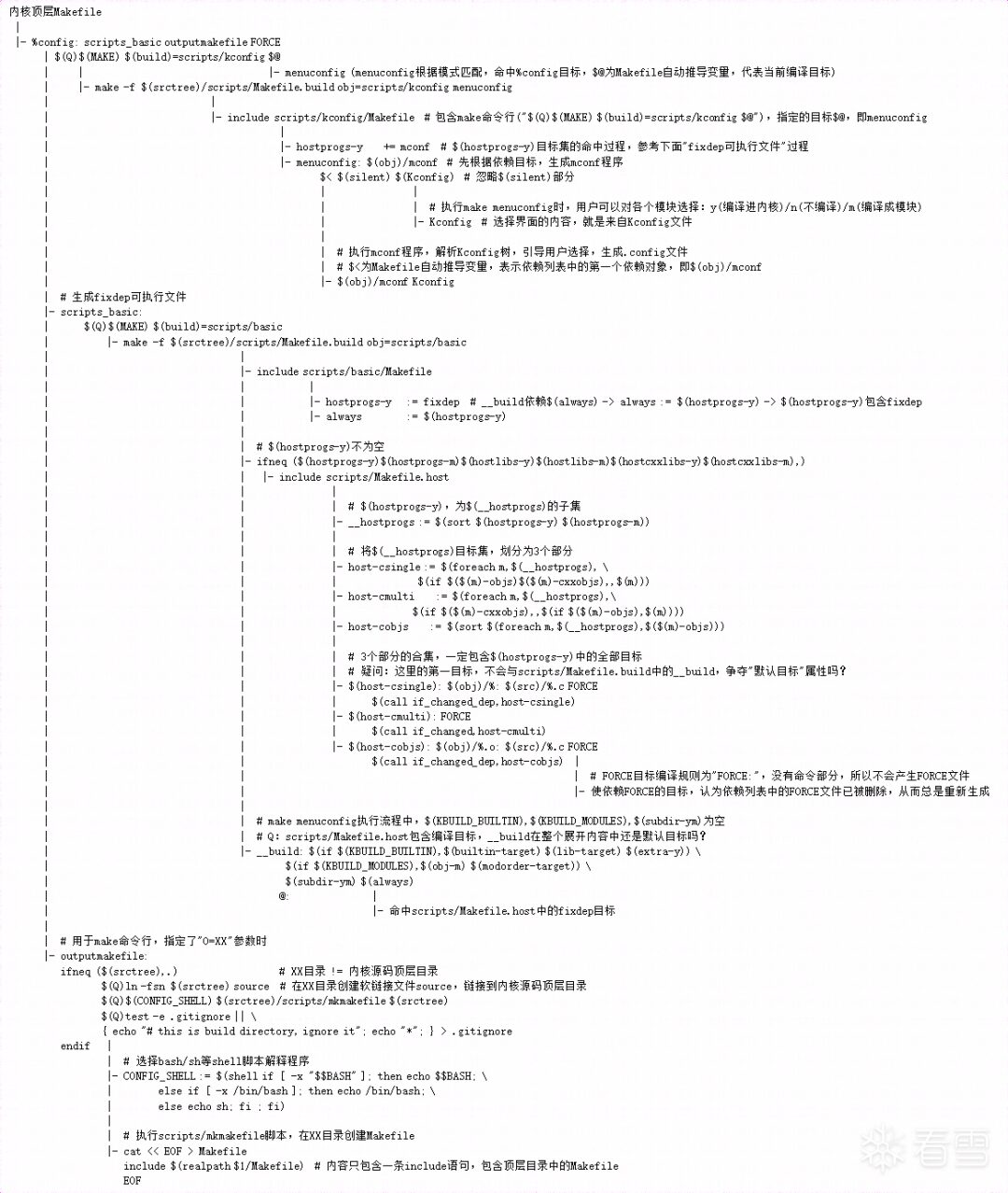

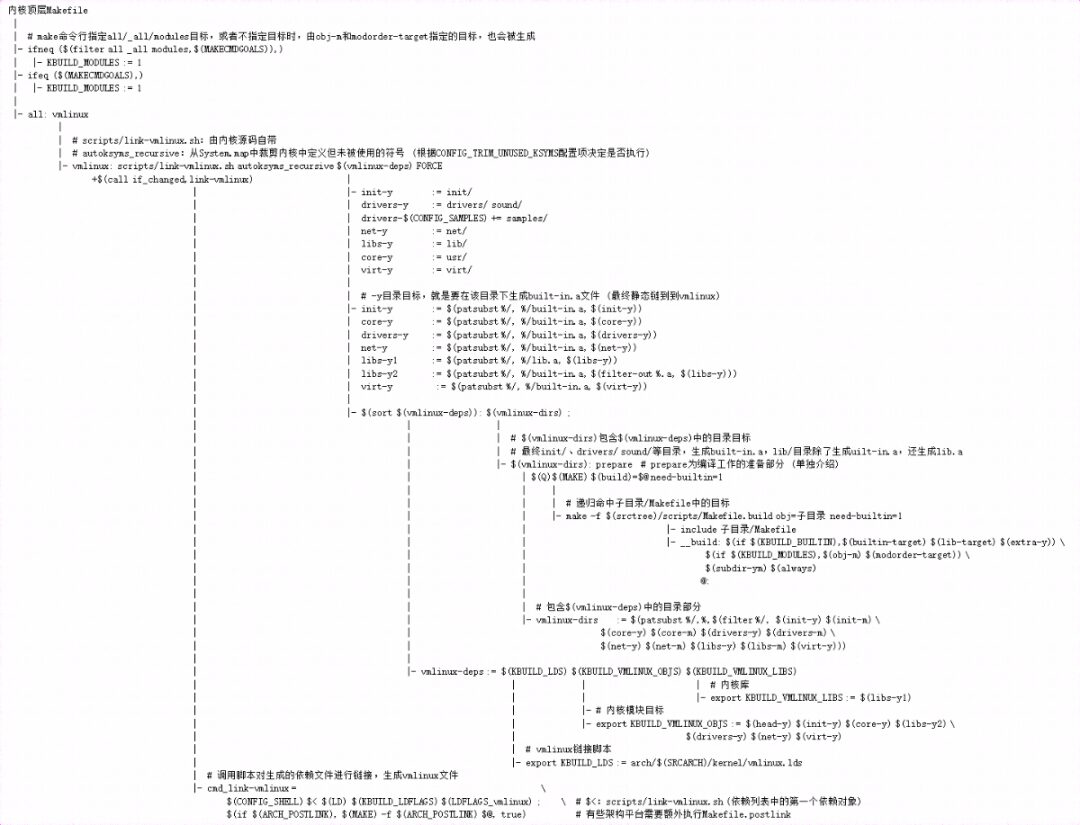

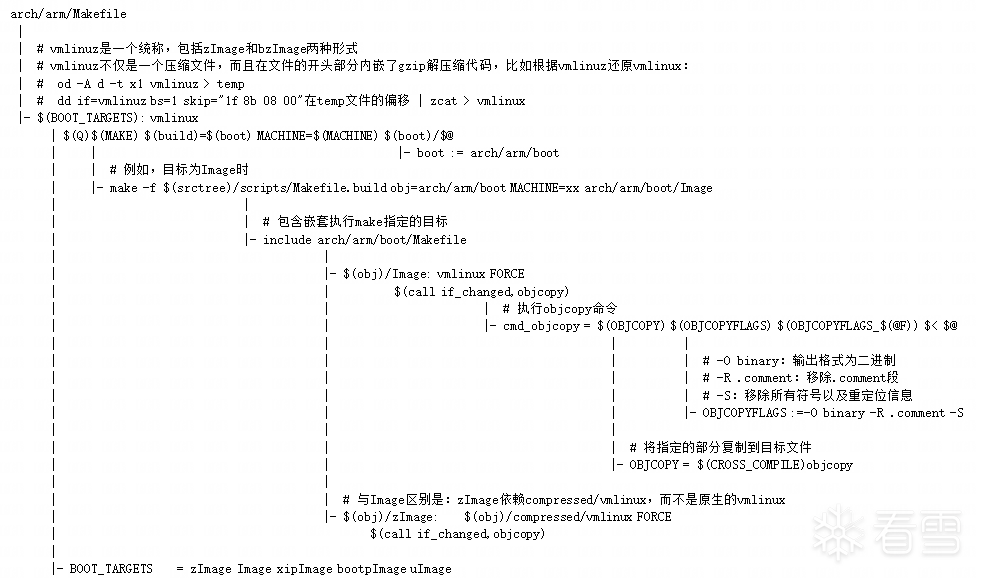

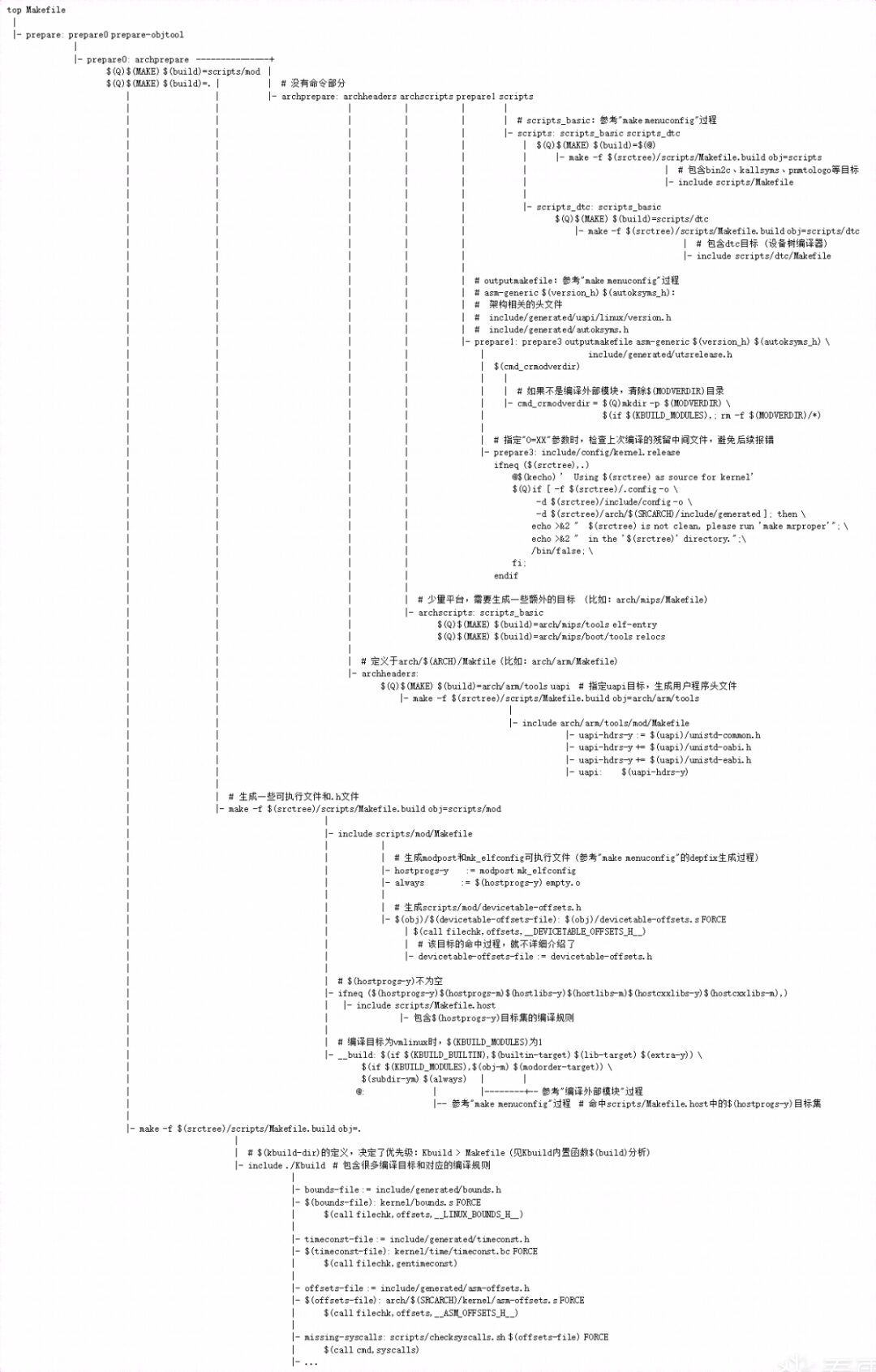

Make [all/_all/modules]

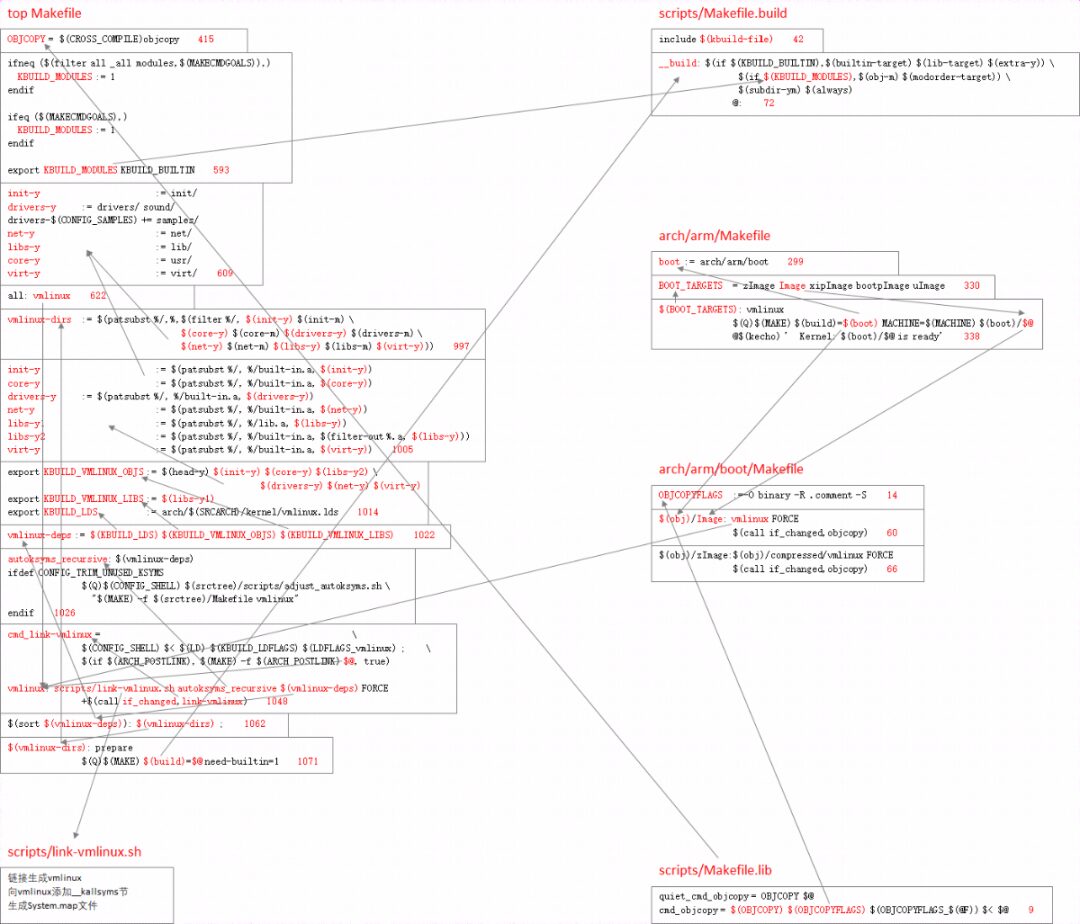

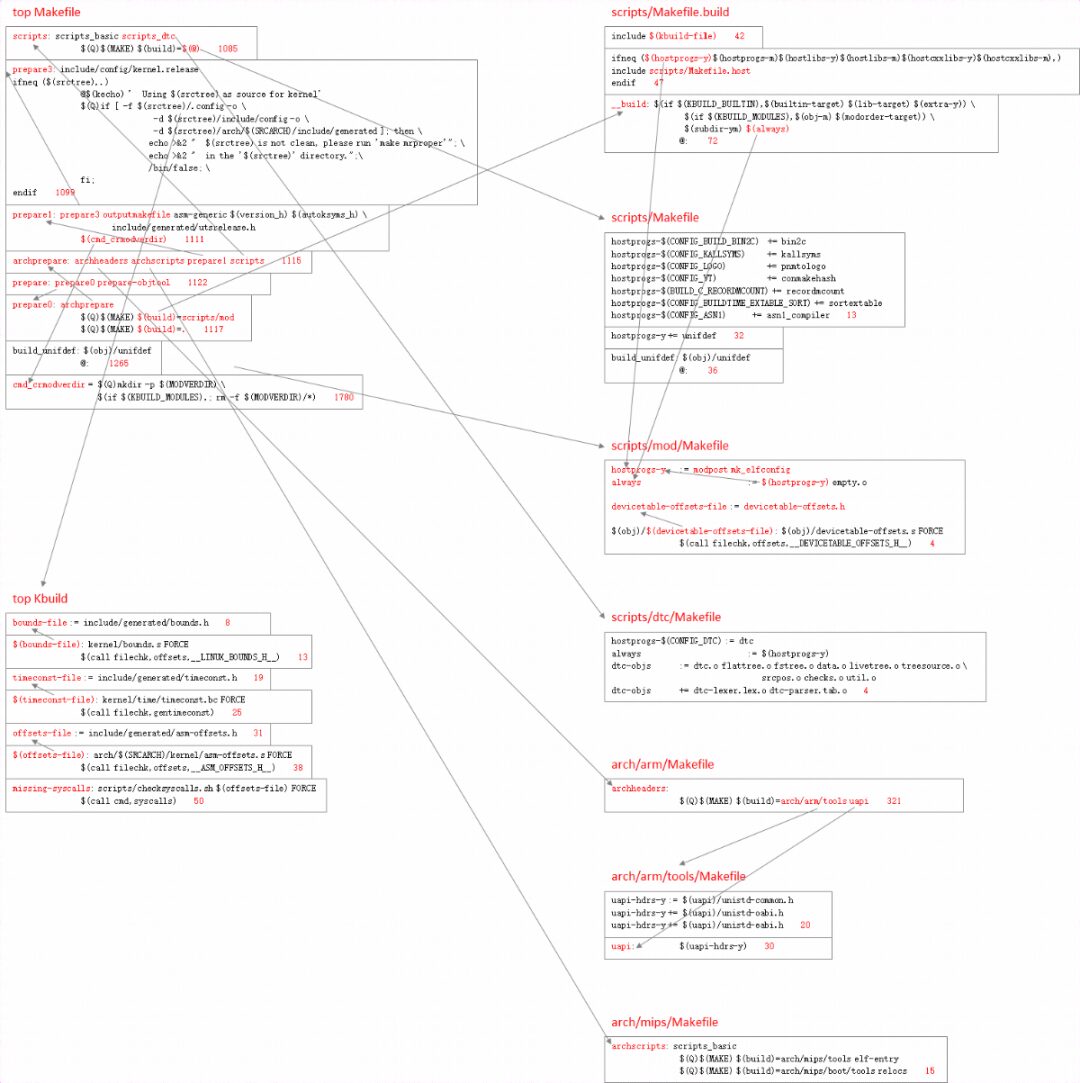

4.1. Related Makefile Content

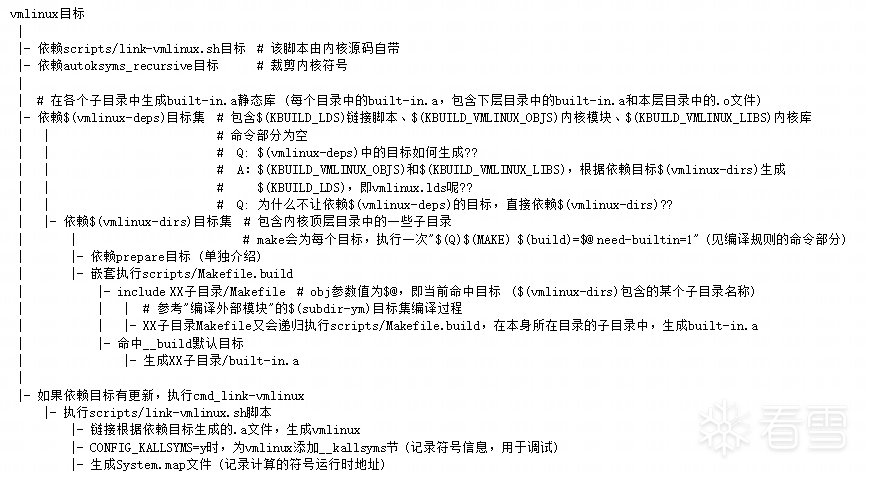

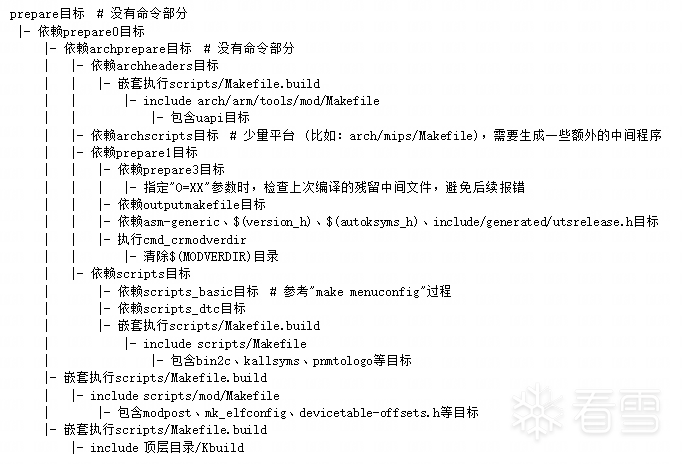

The make command line specifies the all/_all/modules target, or when no target is specified, it is to generate the vmlinux file. The vmlinux target indirectly depends on the prepare target, and the compilation rules of the prepare target are quite extensive, so they are introduced separately:

4.2. Summary Process

4.3. Detailed Process

References

Linux Kbuild Detailed Series:

https://zhuanlan.zhihu.com/p/362640343

Write Makefile with me:https://blog.csdn.net/whitefish520/article/details/103968609

Source: KXue Academy

The article is sourced from the internet, and the copyright belongs to the original author. If there is any infringement, please contact for deletion.

Recommended Reading:

Programming Paradigms in C Language for Linux Kernel (qq.com)

Linux | Kernel Boot Process Source Code Analysis

Understanding Linux Kernel in One Article, Clear and Concise

A Diagram to Understand the Operating Principles of Linux Kernel

Add me on WeChat, scan to join the high-quality embedded group

Follow me 【Learn Embedded Together】, Learning and Growing Together.

If you find the article good, click “Share“, “Like“, or “Looking“!