Microsemi started offering RISC-V soft cores in its FPGAs in 2017, Lattice began in 2020, and Intel (Altera) followed in 2021, making Xilinx the last major supplier to do so (May 30, 2024).

Microsemi and Gowin also have RISC-V hard cores in their FPGAs, similar to Zynq. For Microsemi, a cluster consisting of five 64-bit SiFive U54/S51 cores (four supporting Linux, one “real-time”) runs at 600 or 666 MHz depending on the FPGA grade, essentially a downgraded HiFive Unleashed in an FPGA.

Currently, FPGA manufacturers are leaning towards RISC-V for both hard and soft cores. This is understandable for some “new” manufacturers; however, for established manufacturers like Xilinx or Altera, who already have RISC-based soft cores, why are they also developing RISC-V?

First, let’s take a brief look at the development of RISC-V, and then analyze why these FPGA manufacturers are choosing RISC-V.

Development of RISC-V

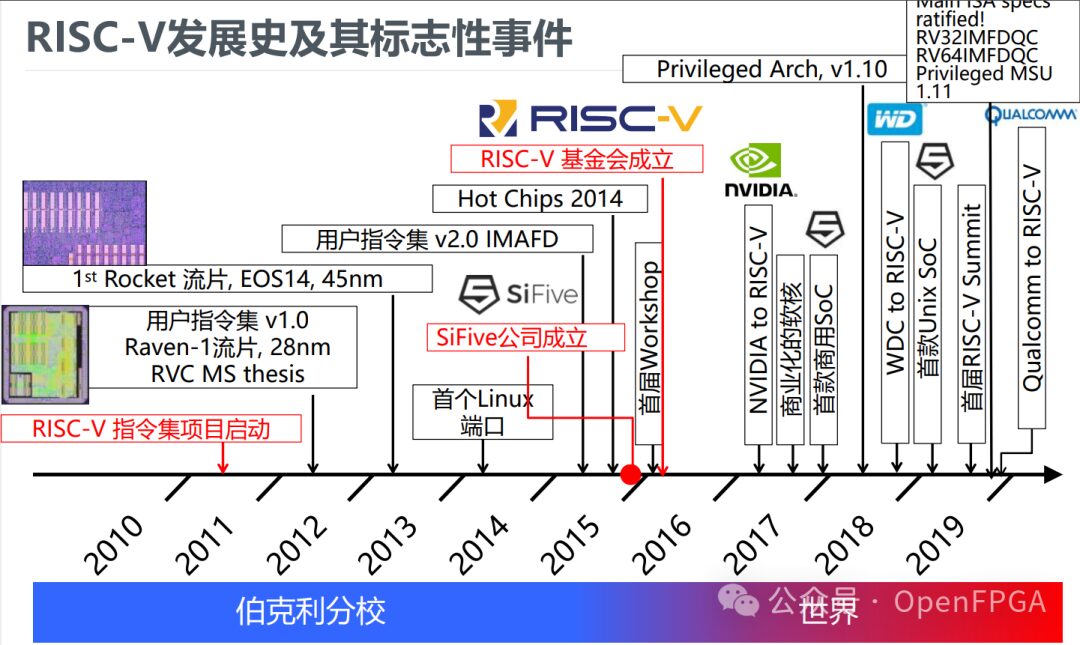

RISC-V (pronounced “risk-five” in English) is an open-source instruction set architecture (ISA) based on the principles of reduced instruction set computing (RISC), which can be simply explained as a type of “open-source hardware” corresponding to the open-source software movement. The project was launched in 2010 at the University of California, Berkeley, with many contributors being volunteers and industry workers outside the university. (Source: Wikipedia)

Its development history and landmark events are shown in the figure below:

Many large companies have already joined the RISC-V “family,” and some of the manufacturers are listed below:

RISC-V vs RISC vs ARM

At first glance, many might think that RISC-V is a variant of RISC, and RISC is a type of instruction set architecture. After all, their names are similar, which can easily lead to confusion. But this is far from the truth. A brief introduction to RISC and RISC-V will clarify their true differences.

What is RISC?

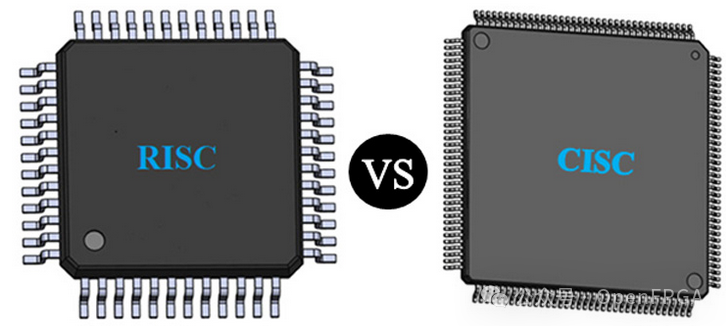

RISC is a broad term that means “Reduced Instruction Set Computer.” Essentially, RISC computers are designed to run simpler single instructions. Compared to CISC (Complex Instruction Set Computer), RISC processors use a uniform instruction length for almost all instructions. In contrast, CISC instructions are more complex and can execute low-level and multi-step operations.

In simple terms, RISC processors can execute simpler, uniform instructions, while CISC can execute instructions of varying complexity and scope. Each RISC instruction can only do one thing at a time, while CISC instructions can do multiple things simultaneously. Since instructions are written in simpler code and are inherently simpler, RISC processors typically require more instructions to complete the same tasks as CISC processors. This difference can be offset by increasing the speed at which RISC CPUs execute these tasks through pipelining. Because they are simpler, RISC processors can be designed faster than CISC processors and can run more efficient code.

Since RISC itself is not an architecture, but a broad term, many CPU architectures can be considered RISC. One of the most famous RISC processor architectures is ARM, which powers our smartphones as well as some laptops and computers. Others include PowerPC, which has long been used in Apple computers and gaming consoles. Meanwhile, x86 can be considered a CISC design due to its complexity.

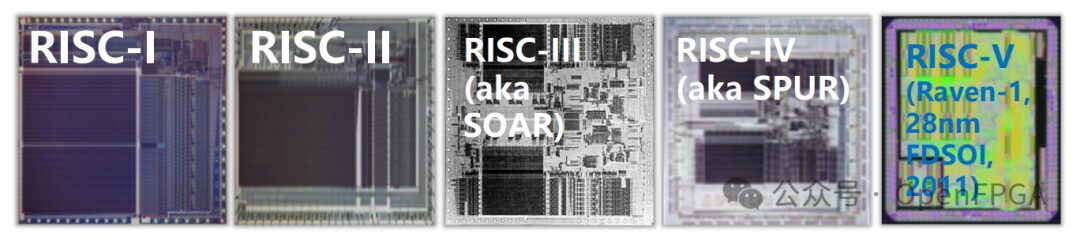

The term RISC was coined during the Berkeley RISC project at the University of California, Berkeley, led by David Patterson from 1980 to 1984. The project proved to be very successful, and the term “RISC” later encompassed all Reduced Instruction Set Computers – even Stanford’s competing MIPS project developed at the same time ultimately became known as RISC architecture. As for that specific Berkeley project, it was later adopted by the SPARC microarchitecture developed by Sun Microsystems – which ultimately inspired the ARM architecture in our smartphones.

What is RISC-V?

While RISC itself is not a specific architecture, it can be confusing to refer to an architecture that uses the RISC name, which is RISC-V. It is an instruction set architecture (ISA) developed at the University of California, Berkeley, designed to embody the principles of RISC processors while also being an open-source standard. While the most famous RISC architecture, ARM, is proprietary and requires licensing from chip manufacturers, RISC-V is free and generally available for anyone to use.

However, unlike ARM, the development and release of RISC-V aim to introduce a CPU design that is open-source, scalable, and deployable on any device without paying royalties. According to the designers, having a free-to-use CPU architecture can significantly reduce software costs.

Thus, comparing RISC and RISC-V is not meaningful; instead, we should compare ARM vs RISC-V.

RISC-V vs ARM

Modeling and Architecture

Historically, ARM has dominated the microprocessor market, from low-power devices to high-performance processors. This is mainly due to its licensing model, which allows companies to license IP and customize it according to their applications. Additionally, ARM has developed multiple series of processors, such as Cortex-A for high-performance applications, Cortex-R for real-time applications, and Cortex-M for energy-saving applications — each series has become an unofficial performance standard for various applications.

On the other hand, the RISC-V architecture is inspired by ARM’s proprietary modeling. Berkeley researchers initially created this architecture as an open-source alternative to promote technological innovation. Since then, it has gained favor from several large tech companies such as Google and Nvidia.

ARM has a mature software and hardware ecosystem that can help companies accelerate their development cycles. It also offers a range of options with mature feature sets. In contrast, the RISC-V architecture provides flexibility and a degree of customization that ARM devices cannot offer. Considering raw performance, ARM will outperform any RISC-V processor. Although ARM continues to maintain its performance lead, RISC-V has proven to offer higher computing density. This means smaller chips with the same performance can be obtained, which is beneficial in many applications, such as wearables like smartwatches.

Openness and Licensing

RISC-V and ARM are both instruction set architectures (ISA). However, their main difference is that RISC-V is an open-source ISA, while ARM is a proprietary ISA (which requires licensing).

Instruction Set

RISC-V has a fixed instruction set architecture that includes a basic integer instruction set and optional extended instruction sets for floating-point operations, vector processing, and other functions. ARM has multiple instruction sets, including ARMv7, ARMv8, and various extensions like NEON for SIMD (Single Instruction, Multiple Data) operations.

Flexibility and Customization

RISC-V offers greater flexibility and customization because it is open-source, allowing designers to tailor the ISA to their specific needs. While ARM provides some level of configurability through its extensions, it is limited by its proprietary nature.

Ecology and Industry

ARM has a well-established ecosystem that includes various processors, development tools, and support from different vendors. It is widely used in mobile devices, embedded systems, and increasingly in servers and data centers. The RISC-V ecosystem is still developing but has gained significant attention, especially in academia, research, and startups. It is also gaining traction in IoT, edge computing, and some server applications.

Performance and Energy Efficiency

ARM has always focused on energy efficiency and has maintained market dominance in this area. They have provided options that focus on energy efficiency and ease of use for low-power devices. Additionally, they offer hardware floating-point and DSP extension options for high-end applications like smartphones.

There are also many energy-saving features available, including dynamic voltage and frequency scaling, which allows processors to reduce or increase chip voltage and clock based on real-time requirements. On the other hand, RISC-V allows for smaller silicon footprint, which gives it a power consumption advantage. Furthermore, the fixed 32-bit instruction format and 16-bit compressed instruction extensions can help achieve more energy-efficient code implementations. Overall, while RISC-V offers the potential for lower power consumption devices, it has not yet reached that level. A significant amount of work and time is still needed before RISC-V starts to capture market share from ARM.

Cost and Accessibility

Implementing RISC-V cores can be more cost-effective for companies since there are no licensing fees associated with ARM. ARM cores typically require licensing fees, which increase the production costs of devices adopting ARM architecture.

Instruction Encoding

RISC-V uses fixed-length instruction encoding, simplifying the decoding logic. ARM uses variable-length instruction encoding, allowing for more compact code, but the decoding logic can be more complex.

FPGA Manufacturers Embrace RISC-V

First of all, whether it’s Altera’s NIOS or Xilinx’s MicroBlaze or Lattice’s LatticeMico8/32, they are all based on RISC. So why have the mainstream FPGA manufacturers basically launched RISC-V based hard or soft cores? I believe these manufacturers mainly consider the following points:

-

Innovation and Development

RISC-V is at its infancy and has great development potential, which can be optimized in terms of power consumption, performance, security, etc., while maintaining compatibility with other designs. At the same time, RISC-V supports custom instructions when acceleration and special functions are needed. Of course, the future development is unpredictable, but entering this field now can secure a place.

-

Fatigue of RISC Soft Cores

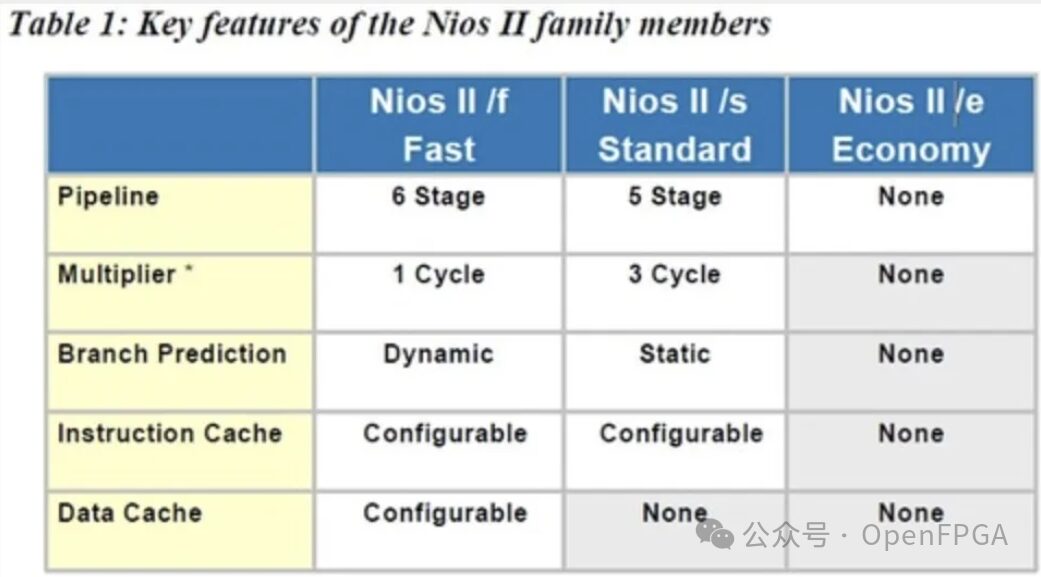

Both NIOS and MicroBlaze have been developed for many years. After years of development, both are relatively stable; however, the structure of FPGA itself limits its performance. In this context, Altera adopted multi-core architecture, and Xilinx gradually evolved from PowerPC to ARM hard cores to gain market acceptance.

-

Ecology

For processors, ecology is the most important. Another reason why soft cores in FPGAs have been lukewarm is ecology. Previously, all manufacturers were “building their own ecology,” leading to the need for systematic learning and adaptation when switching FPGA platforms, and currently, the mainstream ecology in the market is ARM. It is nearly impossible to find a dedicated person who knows NIOS II or MicroBlaze, so currently, FPGA personnel are part-time developing soft cores (which is not a good development direction).

Another issue is that if the ecology is poor or usage is low, it means there are no mature cases to refer to or learn from, let alone porting, and when encountering problems, there is no one to discuss or assist in solving them. Therefore, everyone using soft cores faces a long “newbie period.” Currently, it is necessary to enter a free open-source ISA architecture that may become mainstream in the future.

-

Characteristics of the RISC-V Architecture

In addition to the characteristics mentioned above, RISC-V has another feature – a frozen ISA. This essentially means that it is frozen, and approved optional extensions are also frozen. Due to the stability of the ISA, software development applications can be confidently applied to RISC-V. Software written for RISC-V may run on all similar RISC-V cores. In the future, it is possible that software developed on NIOS-V can be easily ported to MicroBlaze-V.

-

Customizability of FPGAs

We all know that RISC-V instruction sets adopt a structured instruction set definition method, which is very convenient for implementing instruction trimming and extension. One of the advantages of FPGAs is programmability, which fits well with the trimming and extension of RISC-V, allowing for the construction of soft cores that implement any instructions. At this point, we can customize suitable instructions for specific applications (currently FPGA customization), achieving low power consumption processors suitable for our applications with minimal logic. For example, if we only implement simple applications like serial or SPI interfaces, we do not need very complex instructions, while more complex architectures will require more instructions.

-

Strategic Significance

Previously, there were rumors that Arm and NVIDIA were erasing “sparks,” and Intel’s relationship with Arm was shifting from subtle to strange. Therefore, Intel must have some interest in the RISC-V instruction set. There have been rumors online about Intel acquiring SiFive, a provider of RISC-V instruction set based processors, which was later proven to be untrue. The movements of these giants will influence the direction of the entire industry, meaning that to avoid being eliminated in the industry, following or surpassing these industry giants may not be a bad choice.

Conclusion

Currently, mainstream FPGA manufacturers have launched RISC-V based soft cores, indicating that soft processor cores still have their unique roles and strong vitality. The future development is promising, and RISC-V based hard SOC-FPGA is not far away~