In the fiercely competitive global market for mobile, consumer, and automotive electronic systems, low power consumption, high performance, and high reliability are critical factors for product success. To manage these conflicting demands, design teams need to consider a variety of options comprehensively, such as adopting advanced process technology nodes, particularly FinFET-based devices. These advanced technology nodes enable chips to run at faster speeds with lower power consumption while integrating more functions within the same chip size. However, at these process nodes, significant issues arise during the verification of power consumption, noise, and reliability due to the physical characteristics, sizes, shapes, and interconnections of the devices.

For over a decade, Ansys® RedHawk-SC™ has been the industry standard solution for power noise and reliability analysis verification, becoming an indispensable part of the benchmark processes of various foundries. RedHawk-SC offers excellent capacity, accuracy, and simulation coverage characteristics, fully meeting the design needs for sub-7nm designs, especially those requiring FinFET devices, thereby effectively addressing the aforementioned power noise and reliability simulation issues. This white paper will explore various aspects affecting power/signal integrity and IC reliability, while also introducing how to efficiently analyze and resolve these challenges using Ansys RedHawk-SC. This article is an excerpt from the white paper, and the complete content can be downloaded at the end.

Ansys RedHawk-SC

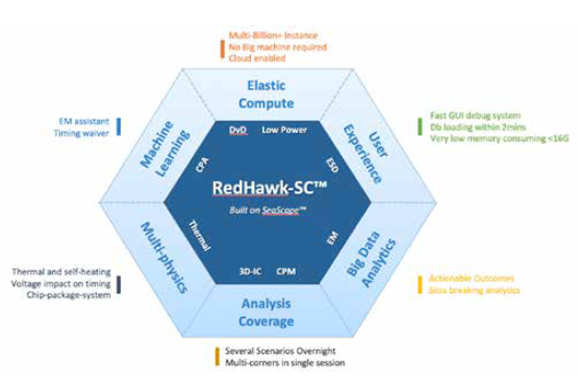

With its scalable architecture, industry-leading engine, and advanced modeling capabilities, Ansys RedHawk-SC is recognized as the industry’s first fully-chip power noise and reliability verification solution certified by foundries. RedHawk-SC can fully meet the demands of advanced sub-7nm devices, such as FinFET and 2.5D/3D structures using Through-Silicon Vias (TSV) packaging technology, thereby further extending the aforementioned capabilities.

Figure 1: Ansys RedHawk-SC Platform

The RedHawk-SC simulation environment enables power noise integrity and reliability analysis from IP, memory, and RTL level to chip-level SoCs (including packaging and PCB). IP and memory designers can not only use Ansys Totem™ to verify designs but also create compact models usable at the SoC level to confirm integration correctness and assess the impact of packaging and full-chip noise on IP.

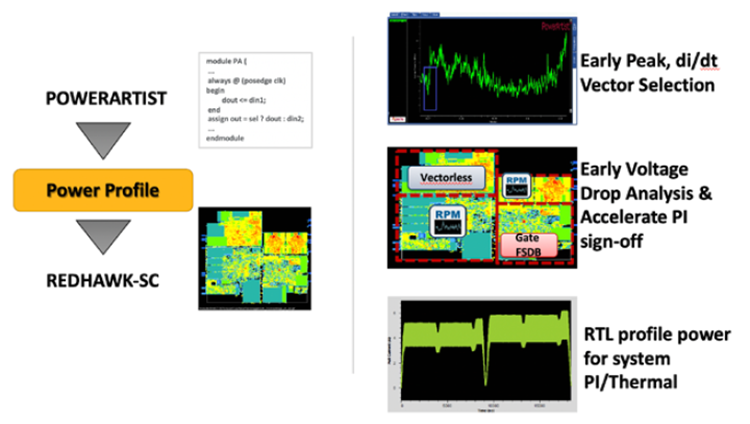

RedHawk-SC provides a comprehensive RTL2Silicon approach that expands the coverage of power noise verification for SoC using data from Ansys PowerArtist™ Design for Power RTL simulations. For designs using advanced process technologies, a broader RTL coverage range and consideration of temperature, packaging, and PCB effects are crucial.

High Capacity and High Performance

To meet the accuracy and verification requirements for implementing large SoC designs at advanced process nodes, comprehensive simulation of the entire SoC and packaging/PCB model is necessary. Without appropriate methods to manage these large simulations, both capacity and turnaround time will surge. Current flows across module boundaries and through on-chip/packaged power and ground interconnect points, while the capabilities of hierarchical modeling approaches are very limited in modeling this time-varying current. Therefore, the predefined current characteristics from hierarchical models cannot accurately reflect the actual operating conditions of the chip.

Chip-Validated Verification Accuracy

Ansys RedHawk-SC features IR/DvD, EM, and ESD integrity verification certifications from leading foundries, applicable to FinFET.

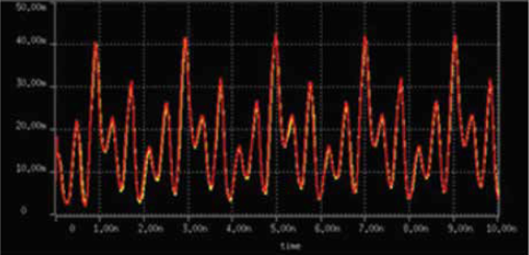

Figure 2: Accuracy: SPICE vs APL

RedHawk-SC can integrate device-level RC parasitics and switching current waveforms using APL and custom macro models (CMM) to achieve full-chip transient simulations with picosecond resolution. These enhanced models meet the evolving accuracy and coverage requirements of today’s complex designs. Figure 2 compares transistor-level SPICE simulation waveforms with corresponding Ansys RedHawk-SC simulations (using the APL model).

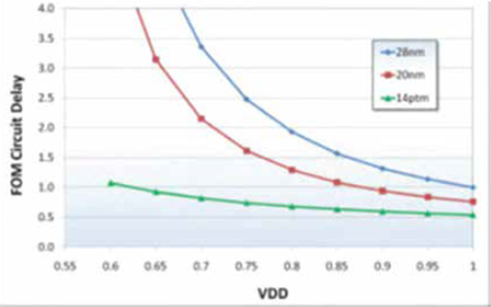

Achieving FinFET Migration

Transitioning designs to FinFET structures can leverage lower dynamic power consumption advantages without affecting standby current. However, the lower supply voltage and higher drive strength of FinFETs reduce noise margins and increase transient noise. Additionally, the localized heating characteristics of FinFETs can raise temperatures, leading to power/signal integrity and EM reliability issues. Moreover, circuit design limitations and the higher current density in FinFET designs can lead to ESD issues, further impacting reliability.

Figure 3: Advantages of Lower Operating Voltage in FinFETs (Source: ARM Rob Aitken)

Today, it is not uncommon for a typical high-performance low-power SoC to have over 100 voltage islands, complex clock and power gating circuits, and dozens of IPs, each operating in different clock and power domains. All these factors necessitate accurate estimation of dynamic voltage drop, thus requiring precise prediction of current across various modes and scenarios in the actual design environment and verification of dynamic voltage drop, with a particular emphasis on understanding the impact of voltage drop and power noise on clocks and critical networks.

Ansys RedHawk-SC

Chip Packaging Analysis (RedHawk-CPA)

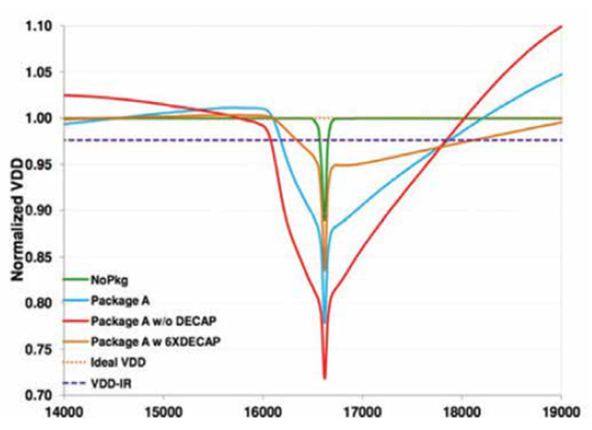

RedHawk-SC includes various IP models detailedly simulated by Ansys Totem. Moreover, accurate verification of today’s low-power, high-performance SoCs requires incorporation of IP models and packaging/PCB parasitic parameters.

Figure 4: Impact of Packaging Parasitics and Decoupling on Chip Power Noise

The integrated chip-package co-analysis solution Ansys RedHawk-CPA accurately analyzes the impact of packaging parasitic parameters on dynamic voltage drop. For designs implemented with advanced process technologies, particularly those using FinFET devices, power analysis should comprehensively consider currents within the packaging, through solder joints, and within the chip. This current can be modulated by variations in supply voltage and interconnect impedance from one time instance to another. This factor, along with others, is crucial for ensuring the validity and accuracy of simulation results.

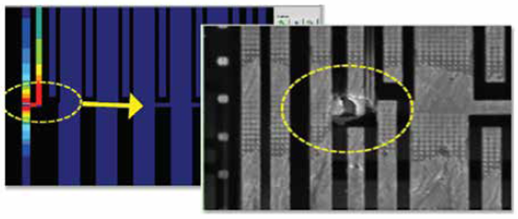

Advanced Reliability Verification

As designs continue to progress towards 5nm and more advanced technology nodes, the issues of electromigration and electrostatic discharge in on-chip interconnections become more severe. Therefore, as the current in wires continues to increase while EM limits decrease, the accuracy and coverage of EM and ESD analysis become extremely important.

Figure 5: Achieving Higher Result Accuracy and Granularity in Full-Chip Power Noise Simulation Using RedHawk-CPA Model (Source: Network Resources)

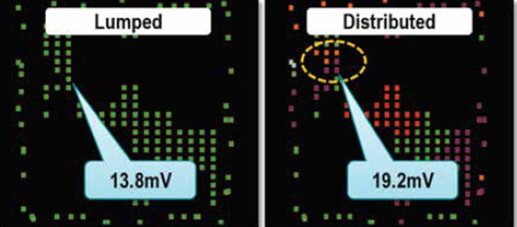

Figure 6: Accurately Predicting Current Values

Figure 7: Increased On-Chip Wire and Through-Fault Failure Due to ESD Events

(Excerpt from Samsung Semiconductor’s Chan-hee Jeon et al.’s contribution to the 2013 International ESD Symposium: EOS/ESD Current Density Analysis Method for Robust I/O ESD Network Design)

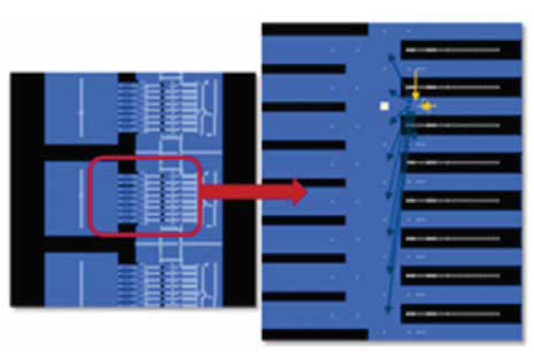

Ansys RedHawk-SC provides comprehensive support for power/ground and signal line EM analysis. It can accurately analyze EM violations while minimizing active error information. The proprietary current-aware extraction method helps create and simulate RLC networks to achieve verification-quality results for every wire and via in the design. As part of the RedHawk-SC platform, Ansys PathFinder-SC™ provides connection and interconnect failure checks for all current paths (wires and vias) in ESD events, thus supporting ESD integrity analysis from IP level to SoC level.

Greater Coverage for Power Noise Convergence

For designs using advanced process technologies, discovering and resolving power noise issues caused by standard cells, memory, I/O, and other IP synchronous switching becomes increasingly important. By employing full-chip transient simulation, RedHawk-SC can accurately predict the dynamic voltage drop noise generated by synchronous switching outputs. RedHawk-SC can combine dynamic switching currents and capacitance models with transistor-level SPICE models using APL or CMM provided by Totem to generate SPICE-level accurate results.

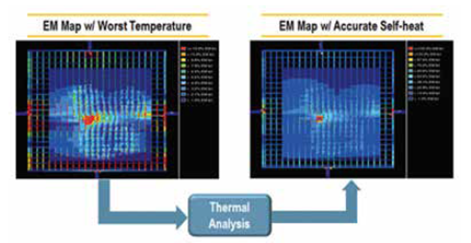

Figure 8: Temperature-Aware EM Analysis for Reliability

To better cover power integrity and reliability issues, identifying design hotspots is crucial even in the absence of input vectors. Ansys RedHawk-SC supports the VectorLess™ dynamic simulation engine, which can automatically generate switching scenarios regardless of whether user-specified full-chip verification constraints are present. Other vector-less modes supported by RedHawk-SC include: PowerTransient™, FrequencyAware™, and VectorLess Scan.

Result Analysis

RedHawk-SC features a fully equipped multi-tab, multi-pane GUI that synchronously displays various results and tables, facilitating better analysis and debugging for users. This layout-based GUI provides the necessary flexibility and robustness for comprehensive user-friendly debugging functions. The multi-pane GUI can provide views of multiple chip layouts, each displaying its power density and direct interactions with one another. By using these multi-pane configurations, engineers can quickly identify the root causes of design weaknesses on the chip and find and isolate modifications that can reduce or eliminate voltage drop or EM hotspot issues. RedHawk-SC allows viewing and analyzing packaging wiring issues within the GUI environment.

Figure 9: Power Noise Convergence from RTL to Silicon to System

Powerful Features of Scalable Ecosystem

Ansys power noise and reliability ecosystem can be further expanded from RedHawk-SC and other related IC simulation platforms to include the following successfully deployed system-level simulation solutions: Ansys SIwave™ (Signal Integrity), Ansys Icepak™ (Thermal Integrity), and Ansys HFSS™ (EMI and High-Frequency Analysis). With these industry-standard multi-physics tools, users can employ system-aware chip simulation methods and chip-package-aware system simulation methods to ensure that chips and systems work together cost-effectively in design.

Conclusion

Ansys RedHawk-SC offers numerous new functionalities and engine-enhanced features. For designs using advanced process technology nodes, these features not only achieve higher performance and shorter simulation turnaround times but also meet stringent verification requirements. For SoC power noise and reliability analysis, RedHawk-SC remains the tool of choice for verification. In addition to analyzing static/dynamic voltage drops and power/signal line EM verification, the RedHawk-SC platform can also perform low-power design simulations, SoC ESD integrity validation, timing (clock, critical path) impact analysis, power grid prototyping, and chip-package-system co-simulation. As the industry-standard verification tool, RedHawk-SC has achieved foundry certification on the latest process nodes, including TSMC’s 3nm FinFET technology. RedHawk-SC has gained the favor and support of thousands of successfully deployed chips.

//

Click to Download the Full Version of This White Paper

“Power Consumption, Noise, and Reliability Verification of System-Aware SoCs”