Follow+Star Public Account, don’t miss the wonderful content

Source | Technology Makes Dreams Greater

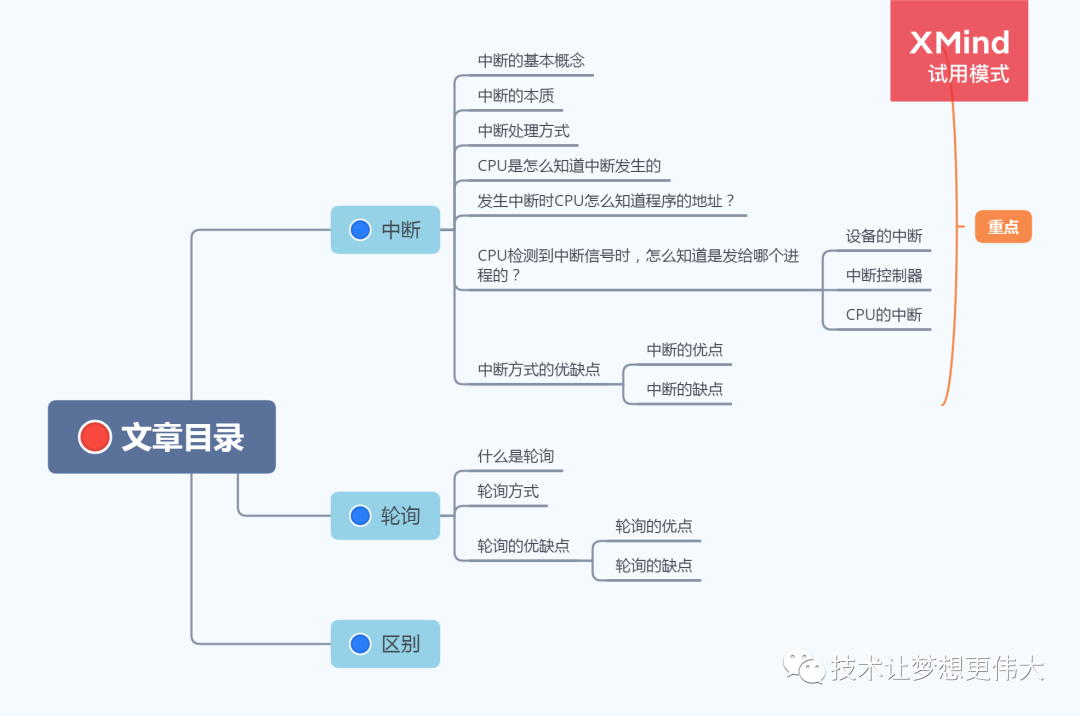

Interrupts

In the process of embedded development, when using a processor, interrupts are an essential element.

Basic Concept of Interrupts

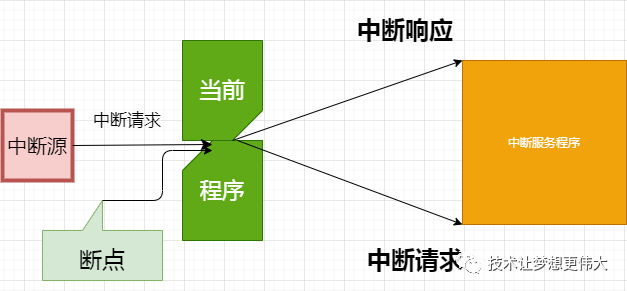

An interrupt is a hardware mechanism that can occur at any time during the CPU’s normal program execution.

Triggered by scheduled arrangements or various random internal and external events, generally referred to as interrupt sources, which send interrupt requests to make the CPU interrupt the currently running program and respond by passing control to the interrupt handler of the service device, a process known as program interruption.

Essence of Interrupts

It is generally believed that interrupts are requests initiated by external devices to the processor, but that is not entirely thorough. Interrupts can be considered as real-time controlled interfaces open to the outside by the processor.

For example, in a computer system, without interrupts, all programs would be deterministic, and we could know the entire process of their operation in advance, unable to interact, equivalent to an accelerator.

With interrupts, external service programs can interrupt the current task.

The CPU’s currently executing program and services that may occur at any time form an asynchronous relationship, where interrupts controlled by humans in real-time are unpredictable.

Interrupts can be seen as a form of hardware polling. Essentially, the CPU will determine the next state of the CPU by reading external signals.

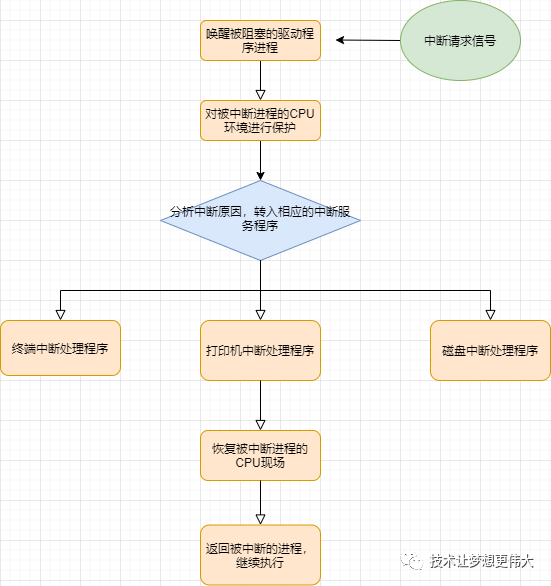

Interrupt Handling

In device management, the relative speed difference between high-speed processors and low-speed input/output devices can reduce overall efficiency. To minimize the waiting time of the CPU in direct control mode and improve the degree of parallel work in the system, it is necessary to adopt interrupt handling.

In the I/O device interrupt mode, the data transmission steps between the CPU and I/O devices are as follows:

-

When a process needs data, it issues a command to start the input/output device, preparing the data to be processed;

-

After the process issues the command to start the device, it gives up the processor and waits for the related I/O operation to complete. At this time, the process scheduler will schedule other ready processes to use the processor.

-

When the I/O operation is completed, the input/output device controller sends an interrupt signal to the processor via the interrupt request line. After the processor receives the interrupt signal, it turns to the pre-designed interrupt handler to handle the data transfer work.

-

The process that has received the data enters the ready state. At some point later, the process scheduler will select this process to continue working.

How Does the CPU Know an Interrupt Has Occurred?

For example, when pressing the Enter key on the keyboard, how does the CPU know I pressed the Enter key and not the Shift key?

First, the CPU does not know which key you pressed; it simply executes machine instructions in order, one by one.

The CPU only knows to execute instructions according to the designed logic, regardless of what the instruction is for.

The operating system knows which key you pressed; it determines whether an interrupt has occurred based on the status of the interrupt controller and corresponding registers.

So when you press a key, the address of that key is immediately written to RAM, and an interrupt signal is sent. The CPU receives the interrupt signal and executes the interrupt program.

How Does the CPU Know the Address of the Program When an Interrupt Occurs?

When an interrupt occurs, the program needs to jump to a certain address to run that segment of the program. Does the CPU need to read the entire memory to find the interrupt vector table?

No, it does not need to read the entire memory, but rather it uses a mapping relationship.

For example, in the x86 architecture, the location of the interrupt vector table is stored in the IDTR register. The CPU can find the interrupt vector table through this register and then locate the specific interrupt entry based on the interrupt number.

How Does the CPU Know Which Process the Interrupt Is For When It Detects an Interrupt Signal?

This question I saw on Zhihu greatly sparked my interest and is very beneficial for our understanding of interrupts.

First, we need to know: interrupts do not directly send data to user processes; interrupts notify the driver and do not care which process is currently executing.

Process operations are the same: save the context, enter the kernel, perform the necessary operations, return to the context before the interrupt, and continue executing the process.

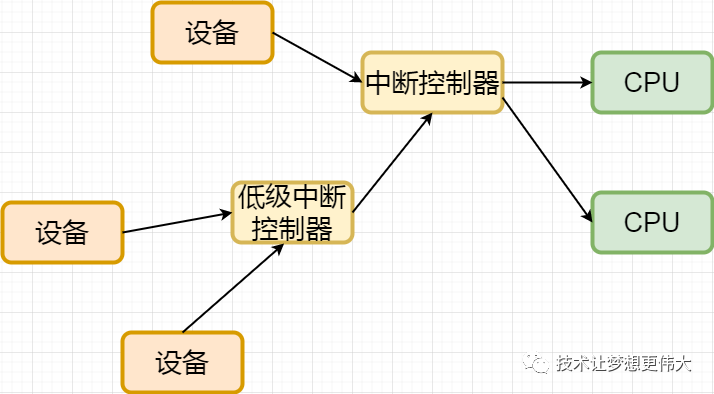

A system’s interrupt system typically consists of components such as device interrupts, interrupt controllers, and CPU interrupts.

Device Interrupts

Refers to the device generating an event to notify the CPU. There are many methods for generating events. To disable interrupts for a device means to stop that device from sending interrupt signals. If the interrupt controller has already received this interrupt signal, it will still report it to the CPU.

Interrupt Controller

Refers to the mechanism for sampling, queuing, and distributing interrupts from multiple devices. To tell the interrupt controller to disable interrupts means to stop it from sending interrupt signals to the CPU (or its superior), regardless of whether the device reports a signal.

CPU Interrupts

Refers to the interrupt line on the CPU core. When this line receives the appropriate level or signal, the CPU core will jump directly from the current execution context to execute the interrupt handler. From the CPU’s perspective, disabling interrupts means not executing the action of “jumping to the interrupt handler”.

Advantages and Disadvantages of Interrupt Mode

Advantages

The I/O device interrupt mode significantly improves CPU utilization;

Supports multiprogramming and parallel operations of I/O devices, enhancing efficiency.

Disadvantages

The increase in the number of interrupts due to various input/output devices operating in parallel through interrupt handling can lead to the CPU being unable to respond to interrupts;

If an interrupt occurs after the buffer is filled with data, it can lead to many interruptions during data transfer, consuming a lot of CPU processing time.

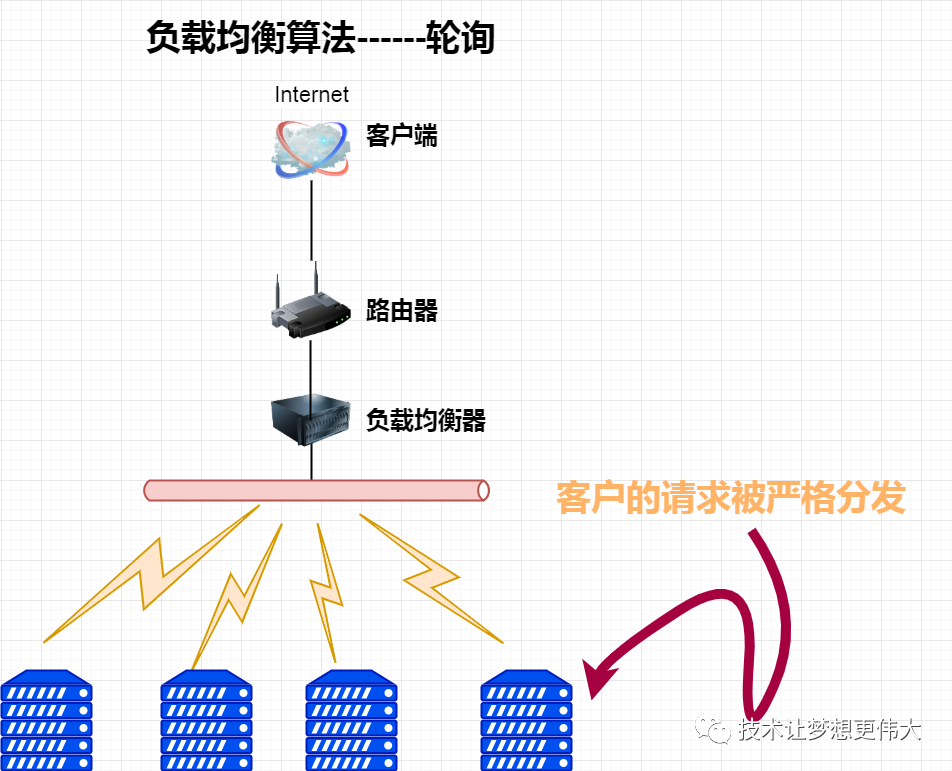

Polling

What is Polling?

Polling is a method by which the CPU decides how to service peripheral devices.

During polling, the CPU periodically issues queries, sequentially asking each peripheral device whether it needs service.

Each device has a bit indicating whether it is ready for service, indicating the status of that device.

When this status is ready, service is provided, and after completing service, the next peripheral is queried, continuing in this manner.

Polling Method

The program polling of I/O devices is a management method for I/O devices in a computer system. It periodically queries each device in turn to check for processing requests.

After querying in turn, if there are requests, they are processed.

After processing the I/O device requests, the processor returns to continue working.

Advantages and Disadvantages of Polling

Advantages

In some applications, it enhances the real-time nature of the program…

Disadvantages

The number of input/output devices that can be handled is also limited.

Polling occupies CPU processing time, resulting in lower efficiency.

Differences Between Interrupts and Polling

-

In interrupts, devices notify the CPU to pay attention; while in polling, the CPU consistently checks devices for attention.

-

Interrupts are not a protocol, but a hardware mechanism; polling is the opposite.

-

In interrupts, the interrupt handler provides service to the device; in polling, the device is maintained by the CPU.

-

Interrupts can occur at any time; polling occurs at regular intervals.

-

In interrupts, the interrupt request line indicates that the device needs maintenance; in polling, the command ready bit indicates that the device needs maintenance.

-

In interrupts, once any device interrupts, the processor is disturbed; in polling, the processor wastes countless cycles by repeatedly checking each device’s command ready bit.

On the Shoulders of Giants

Selected Tutorials from the Embedded Column

Selected Summary | STM32, Microcontrollers

Selected Summary | RTOS, Operating Systems

Click “Read Original” for more shares, and feel free to share, bookmark, like, and view.