Introduction to Embedded Networking

Network Hardware Interfaces in Embedded Systems

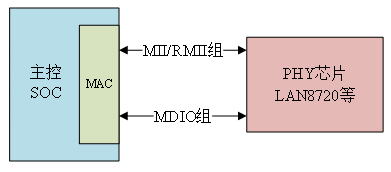

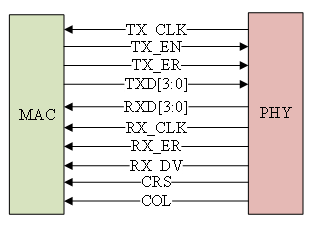

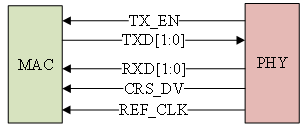

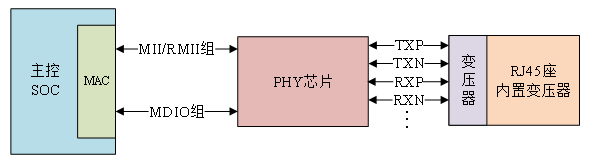

When we mention networking, the hardware that usually comes to mind is the “network card.” Nowadays, the network card is typically accomplished through a chip. Embedded network hardware is divided into two parts: MAC and PHY. People generally refer to the datasheet to determine whether a SOC supports networking. If a chip’s datasheet states that it supports networking, it usually means that this SOC has an integrated MAC, which is similar to peripherals like the I2C controller or SPI controller. However, having just a MAC is not sufficient to drive a network; another chip, the PHY, is also required. Therefore, for SOCs with an integrated MAC, an external PHY chip must be paired. For SOC chips without an internal MAC, an external MAC + PHY integrated chip is needed, leading us to two common embedded network hardware solutions.

1.SOC Without an Internal Network MAC Peripheral

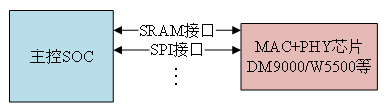

For SOC chips without an internal MAC, external MAC + PHY integrated network chips can be used to achieve network functionality. For example, the DM9000 is commonly used in Samsung Linux development boards, providing an SRAM interface to the SOC, which operates the DM9000 in SRAM mode.

Some external network chips are even more powerful, integrating a hardware TCP/IP protocol stack and providing an SPI interface, such as the W5500. This is generally used in microcontroller applications, where the microcontroller communicates with the W5500 via the SPI interface. Since the W5500 has a built-in hardware TCP/IP protocol stack, the microcontroller does not need to port a software protocol stack and can directly operate the W5500 through SPI, simplifying the microcontroller’s networking solution.

The advantage of this solution is that it allows SOCs that do not support networking to find alternative ways to achieve network functionality. However, the downside is that network efficiency is not high since typically, chips with integrated MACs have network acceleration engines, such as dedicated DMA, which significantly enhance network processing efficiency. Moreover, such chips generally do not support fast networking speeds, usually limited to 10/100M. Additionally, compared to PHY chips, these chips tend to be more expensive with fewer options available.

The connection between the SOC and the external MAC + PHY chip is shown in Figure 1-1:

Content Summary

With the rapid development of semiconductor technology and chip technology, the prices of MPU chips capable of running embedded Linux systems are continuously decreasing. ARM architecture chips are widely used in mobile phones, industrial control, IoT, and autonomous driving. Areas that previously relied heavily on MCUs are now starting to adopt embedded Linux systems. Applications such as card gate machines and automotive charging station operation panels, as well as IoT gateways, all feature embedded Linux, leading to a sharp increase in demand for embedded Linux development talent. Compared to microcontroller development, embedded Linux development is significantly more challenging, particularly in driver development. The embedded Linux kernel is designed with an object-oriented approach and has developed numerous driver frameworks. Developers must master these frameworks to write drivers that meet embedded Linux requirements. This book covers everything from basic LED programs to network driver development, encompassing the three main types of Linux drivers: character device drivers, block device drivers, and network device drivers. A key feature of this book is its comprehensive coverage of device tree development, with the exception of a few initial examples demonstrating how to operate chip registers without using a device tree; all other examples utilize device trees, covering common peripherals in embedded Linux driver development. This book serves as a learning and reference guide for engineers engaged in embedded development, IoT, industrial control, and can also be used as a textbook for courses in computer, electronics, and automation majors related to embedded systems, microcomputer interfaces, and IoT.

Share、Like and Watchat least give me one~

Share、Like and Watchat least give me one~