Keywords: DWT, DEMCR

Table of Contents

1. Introduction

2. Research

3. Enabling DWT for Counting

4. Conclusion

01

Introduction

When using the STM32H7, the customer wants to utilize DWT counting to measure code execution time and evaluate execution efficiency. The customer found that after power cycling or resetting, they could not enable DWT for counting.

02

Research

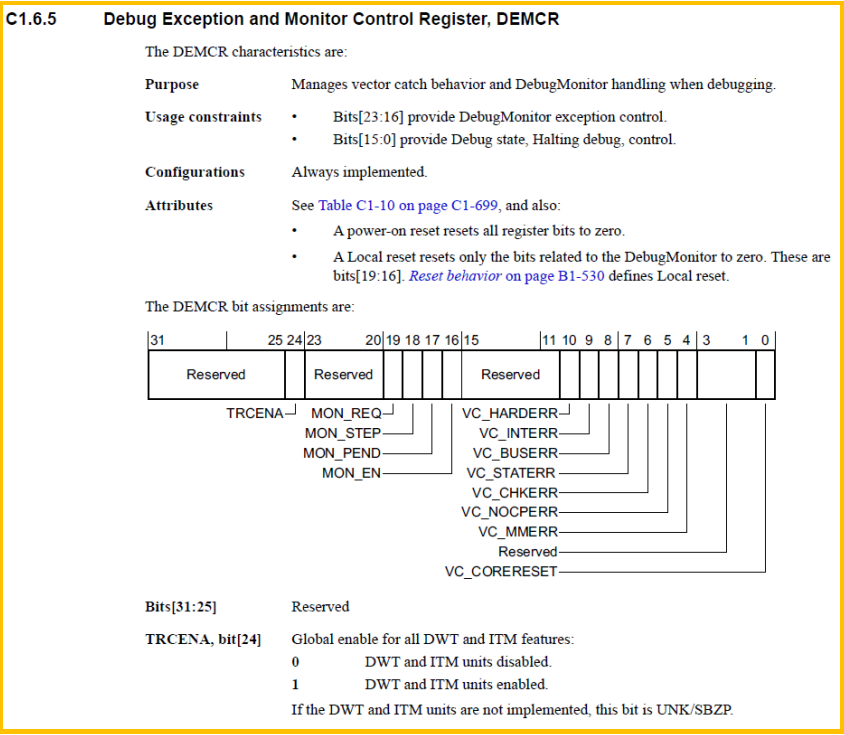

In the ARMv7-M architecture, there is a DEMCR register that controls the enabling of DWT. After a power-on reset, all bits of this register are set to 0. When bit[24] is 0, both DWT and ITM modules are disabled. Therefore, to enable the DWT module, bit[24] of DEMCR must be set to 1, as shown in Figure 1:

Figure 1. DEMCR Register

03

Enabling DWT for Counting

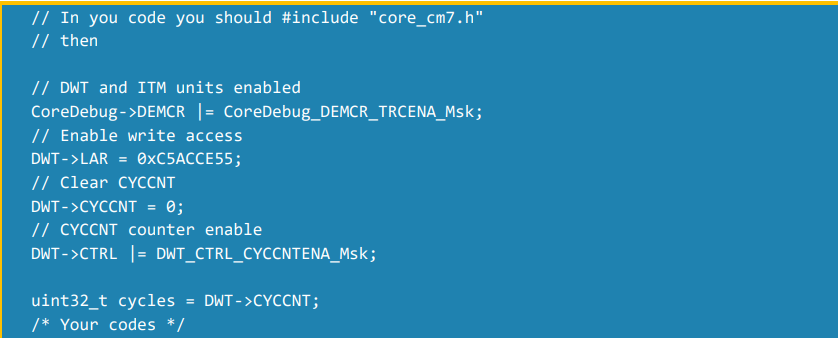

The STM32H7 is based on the Arm Cortex-M7 core, and since Cortex-M7 is part of the ARMv7-M architecture, the H7 must set bit[24] of DEMCR before configuring the DWT module. In Cortex-M7 based chips, DWT-LAR must be used to unlock DWT (other cores may not require this, and should be analyzed specifically), and then the DWT_CTRL can be enabled accordingly.

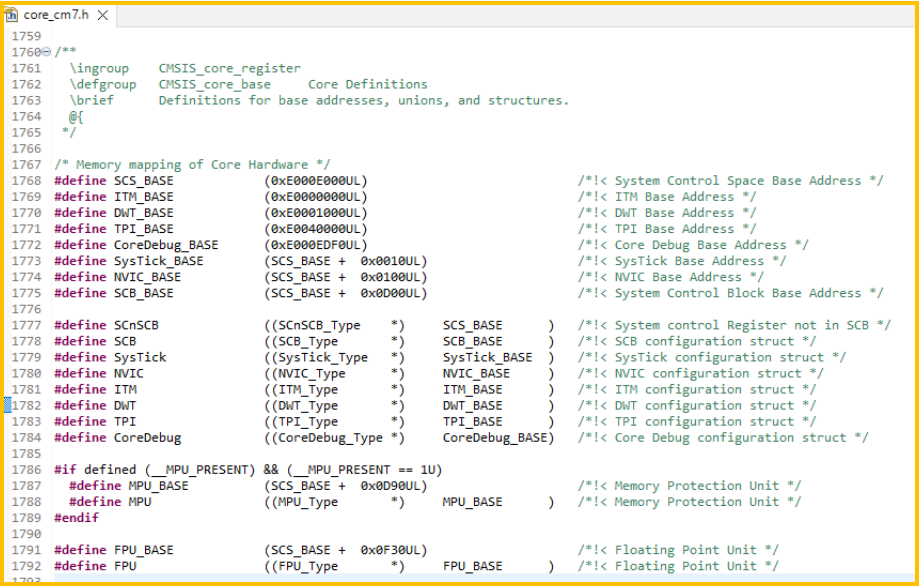

The CMSIS files provide macros for the relevant registers (for example, the “core_cm7.h” file includes macros for DWT and DEMCR), allowing us to configure them conveniently, as shown in Figure 2:

Figure 2. core_cm7.h File

Example (as follows): Using DWT to measure the number of clock cycles used for code execution.

04

Conclusion

When using STM32 based on the ARMv7-M architecture, ensure that bit[24] in DEMCR is configured (enabling DWT) before using DWT.

For more content, feel free to click the “Read Original” link below to download the complete document.

For the complete content, please click “Read Original” to download the original document.