Hello everyone, welcome to my Smart Space. Let’s embark on an immersive learning journey into embedded systems together.

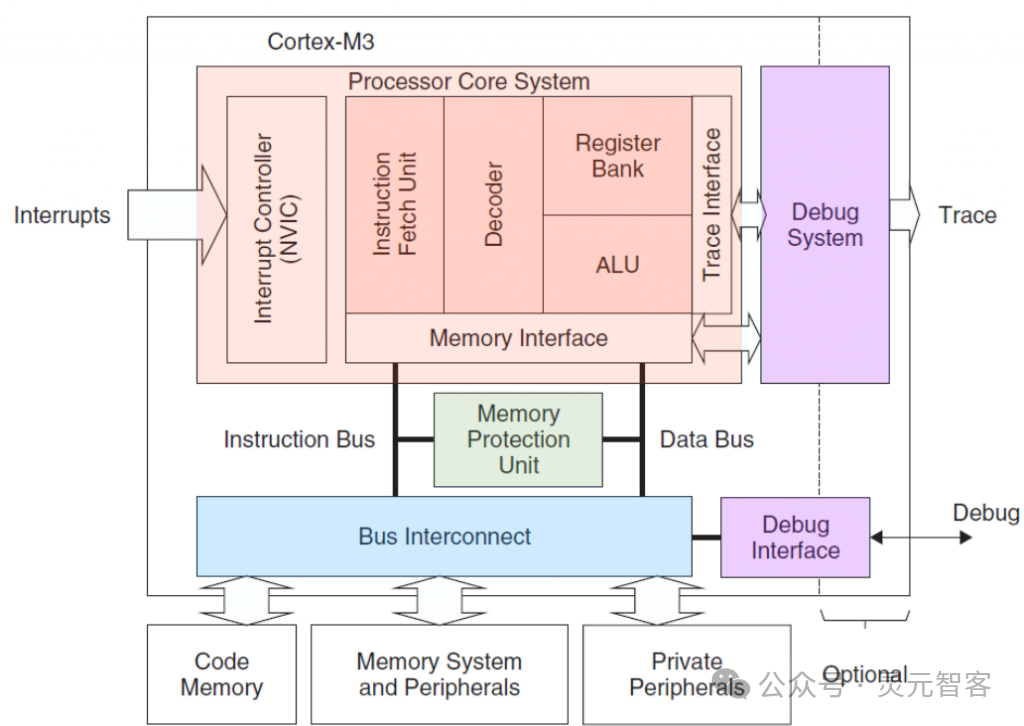

The Cortex-M3 is a 32-bit processor core with a 32-bit internal data path, 32-bit registers, and a 32-bit memory interface. The CM3 adopts a Harvard architecture, featuring separate instruction and data buses, allowing instruction fetching and data access to occur in parallel. This means that data access does not occupy the instruction bus, thereby enhancing performance. To achieve this feature, the CM3 contains several bus interfaces, each optimized for its specific application scenario, and they can operate in parallel. However, on the other hand, the instruction bus and data bus share the same memory space (a unified memory system). In other words, having two buses does not increase the addressable space to 8GB.

Figure 1: A simplified view of the Cortex-M3

References

Cortex-M3 Authority Guide (Chinese Reference) — Authored by Joseph Yiu, Translated by Song Yan

Reference link:

https://www.ilinkros.cn/?p=66