Source: Synopsys Technology Zhihu, thank you!

Source: Synopsys Technology Zhihu, thank you!

1

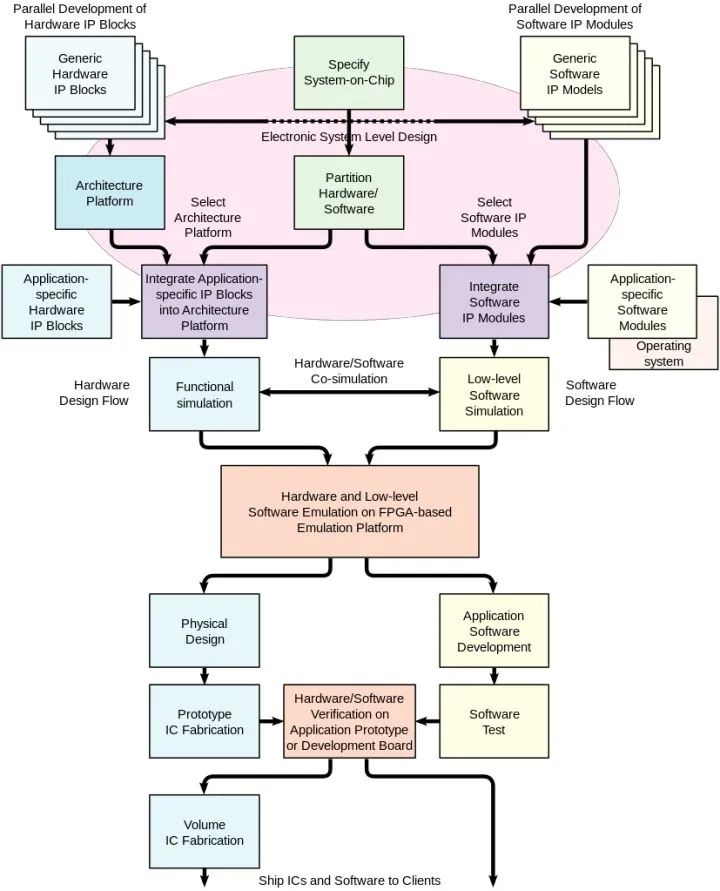

The First Challenge: Difficulty in Architecture Design

2

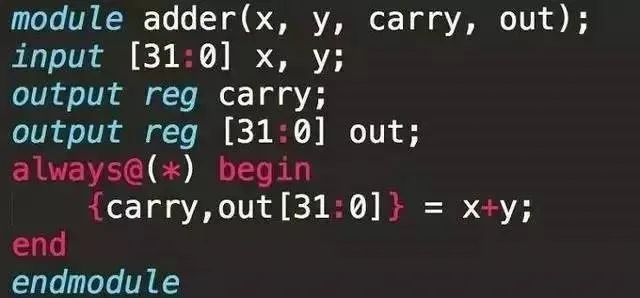

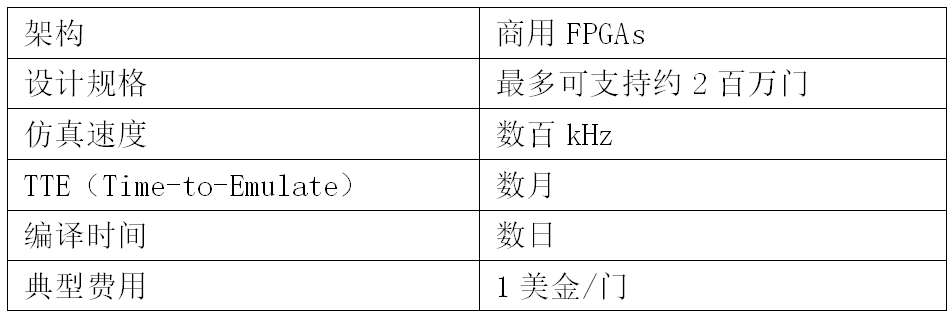

The Second Challenge: Difficulty in Verification

3

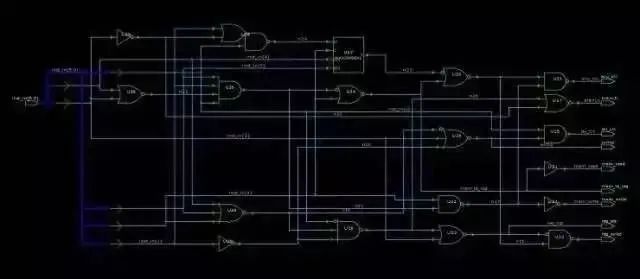

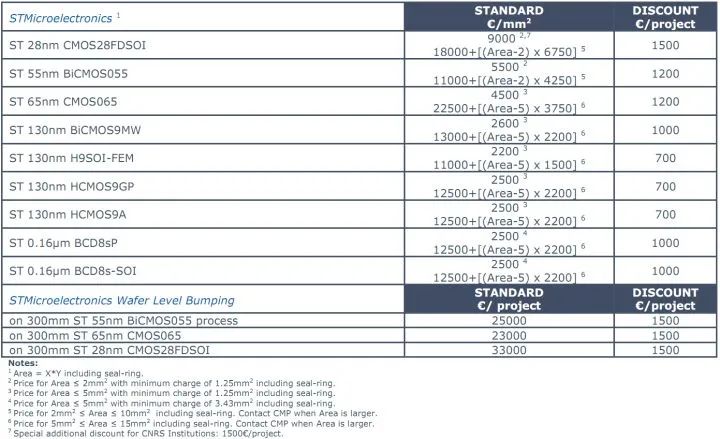

The Third Challenge: Difficulty in Tape-Out

4

The Fourth Challenge: Increasingly Challenging Design Requirements

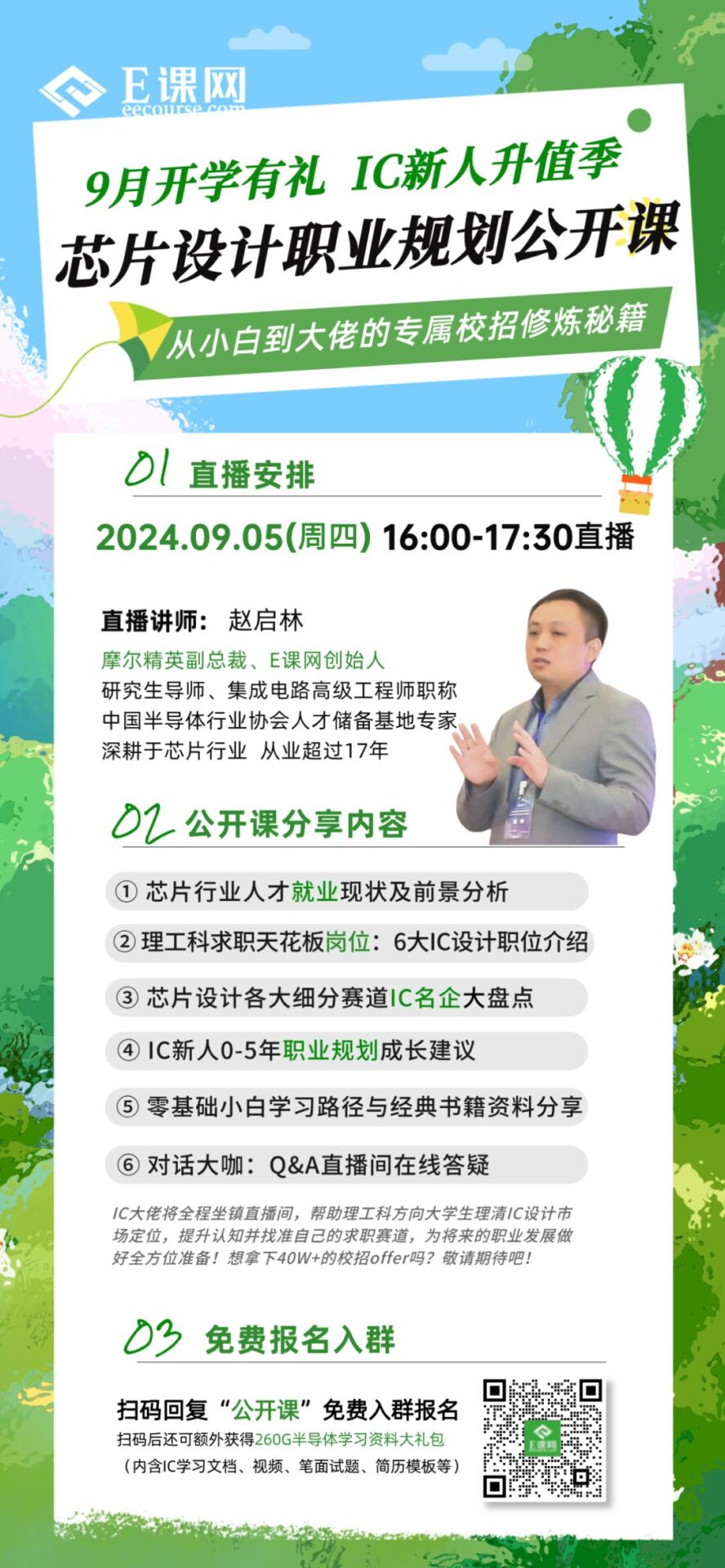

E-course Network (www.eecourse.com) is a professional integrated circuit education platform under Moore Elite, dedicated to cultivating high-quality integrated circuit professionals in the semiconductor industry. The platform provides a training environment that aligns with corporate needs, offering a comprehensive curriculum and practical training through both online and offline methods, rapidly developing students to meet corporate demands.

Founded in 2015, E-course Network has a mature training platform, a complete course system, and a strong faculty. It plans to establish a premium semiconductor course system with 168 courses, covering the entire integrated circuit industry chain, and has 7 offline training bases. E-course Network has a total of 517,000 fans, directly supplying 8,127 professionals to the industry. It has established deep cooperative relationships with 85 universities and has held 240 corporate training sessions.