With the arrival of the post-Moore era, advanced semiconductor processes have been widely applied to FPGAs. Popular applications of FPGAs today include autonomous driving, 5G, artificial intelligence, edge computing, machine learning, video and image processing, the Internet of Things, aerospace, and military.

Taking autonomous driving as an example, with the evolution and upgrading of technology, the complexity of the underlying technologies is also continuously increasing—multi-sensor fusion, larger computation algorithms, high-speed data processing, embedded terminals and devices, machine vision, voice control, deep learning inference… all of which make it impossible for CPU and GPU computing power to cope alone; meanwhile, the high one-time engineering (NRE) costs make ASIC design unable to handle frequent technological evolution. Therefore, the combination of high computing density and high flexibility FPGAs has gradually become the mainstream approach. In addition, the high reliability of autonomous driving technology and the demand for rapid and continuous iteration also require early realization and verification in FPGA design.

The pressure of product launch and development cycles has made “how to improve the overall design efficiency and reliability of FPGAs” a key focus for engineers.Enhancing efficiency and reliability is driven by verification methodologies that are key.

Research by Wilson Research Group indicates that due to the increasing complexity of design and verification, the average verification time for FPGAs has occupied half of the project cycle, with more than 60% of development projects unable to be delivered on time, and over 80% of delivered projects containing bugs. As a result, EDA vendors are gradually guiding FPGA designers to adopt methodologies similar to chip design to improve the efficiency and productivity of FPGA design verification, thereby accelerating time to market.

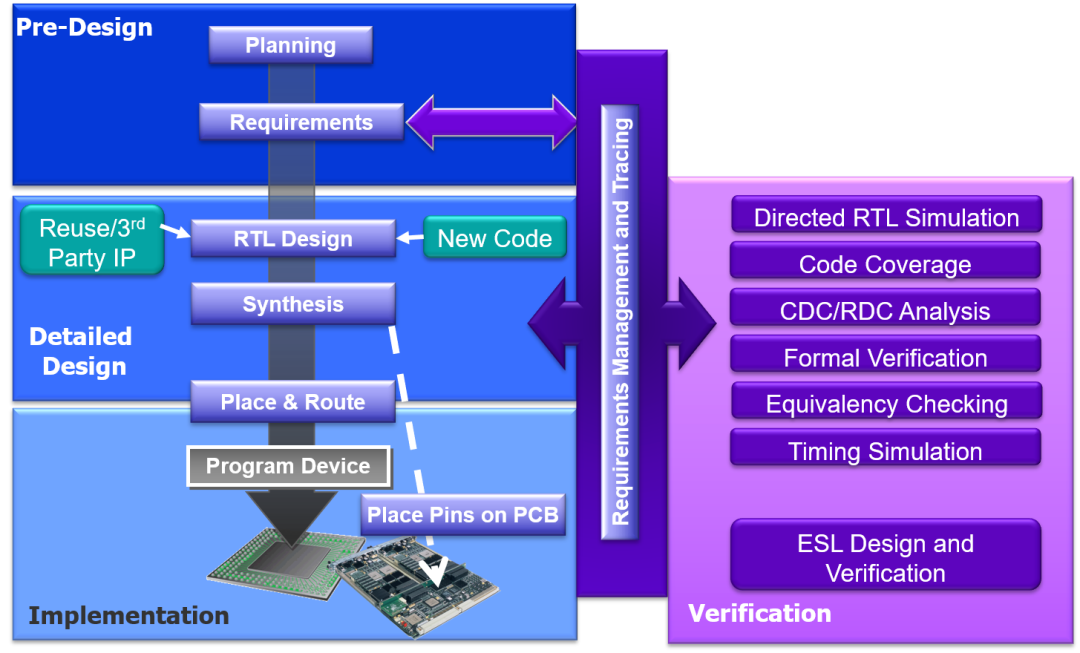

Currently, the development process of complex FPGA hardware electronic devices involves numerous steps and phases, generally including preliminary design, detailed design, and implementation stages, with verification present at each stage. Therefore, a complete set of efficient collaborative working, demand-driven design concept technologies and methodologies must be introduced during the design process.

The demand-driven high reliability FPGA design method means that the center of the design process will revolve around how to capture and confirm design requirements, and how to design, verify, and implement based on those requirements. Under this high reliability demand, more and more FPGA designers are beginning to utilize chip design and verification technologies, considering them at the electronic system level, and then performing high reliability design, verification, and implementation at the register transfer level (RTL), comprehensively improving FPGA development efficiency, ensuring that every step of FPGA development can be traced back to the initial requirements. This improvement in technology and methodology can help FPGA engineers use advanced design, verification, and implementation technologies to accelerate FPGA development and achieve higher quality designs.

To address the increasing complexity of FPGA verification and improve design verification efficiency and quality, Mentor PCB has brought to FPGA designers a comprehensive solution covering the entire FPGA design process—from ESL system modeling, architecture analysis, and hardware-software co-verification, high-level synthesis, to comprehensive code checks, cross-clock domain analysis, dynamic simulation, and static formal verification functional validation, safety synthesis, all the way through to collaborative design with FPGA synthesizers and PCB pins, efficiently completing the overall design and verification of FPGA projects.

On May 7, Mentor’s experts will communicate with you online! Long press to identify the QR code below to sign up for an appointment and learn more about the hardcore knowledge of high reliability FPGA overall design, verification, and implementation!