In embedded system development, driver design is a key factor affecting system performance, energy efficiency, and maintainability. Below is an in-depth analysis of three mainstream driver design techniques along with practical recommendations:

1. Polling Driver

Technical Features:

-

Blocking Design: The main program cannot perform other tasks while waiting for peripheral responses.

-

Simple Implementation: Only requires looping to check the status register flags.

-

Low Resource Overhead: No need to configure interrupt controllers or DMA channels.

Typical Application Scenarios:

-

High-speed peripherals (e.g., GPIO state detection)

-

Initialization phase or single operations

-

Simple devices with very low real-time requirements

Blocking Design:

// Blocking polling example

bool Adc_GetResultsBlocking(uint32_t AdcResults) {

Adc_Start();

while(ADC_COMPLETE_FLAG == FALSE);

AdcResults = Adc_ReadAll();

return AdcResults;

}Optimization Strategies:

// Non-blocking polling example

bool Adc_GetResultsNonBlocking(AdcResults_t* results) {

if(ADC_COMPLETE_FLAG) {

*results = Adc_ReadAll();

return true;

}

return false;

}Advantages: Allows the main program to perform other tasks while waiting.Challenges: Requires a well-designed polling interval to avoid wasting CPU resources.

2. Interrupt-Driven

Core Mechanism:

-

Event-triggered (e.g., UART reception complete)

-

Timed scheduling (e.g., ADC periodic sampling)

Key Implementation Points:

-

Interrupt Service Routine (ISR) Optimization:

// UART receive interrupt example

volatile uint8_t uart_rx_buffer[256];

volatile uint16_t uart_rx_index = 0;

void UART0_IRQHandler(void) {

if(UART0->ISR & RXNE_FLAG) {

uint8_t data = UART0->RDR;

if(uart_rx_index < sizeof(uart_rx_buffer)) {

uart_rx_buffer[uart_rx_index++] = data;

}

// Trigger application layer processing event

event_flag |= UART_RX_EVENT;

}

}2. Interrupt priority management (based on NVIC controller)

3. Critical section protection (disable interrupts)

Design Best Practices:

-

Keep ISR execution time under <10μs

-

Use double buffering to avoid data contention

-

Communicate with the main program through event flags

-

Prefer a composite mode of DMA transfer and interrupts

3. DMA-Driven

Architectural Advantages:

-

Zero-copy data transfer

-

Hardware-level concurrency control

-

Batch processing capability

Typical Configuration Process:

void ConfigureDmaForAdc(void) {

// 1. Configure DMA channel

DMA1_Channel1->CCR = DMA_CCR_MINC // Memory address increment

| DMA_CCR_TCIE // Transfer complete interrupt

| DMA_CCR_DIR_M2P; // Memory to peripheral

// 2. Set transfer parameters

DMA1_Channel1->CNDTR = ADC_BUFFER_SIZE;

DMA1_Channel1->CPAR = (uint32_t)&(ADC1->DR);

DMA1_Channel1->CMAR = (uint32_t)adc_buffer;

// 3. Enable DMA interrupt

NVIC_EnableIRQ(DMA1_Channel1_IRQn);

NVIC_SetPriority(DMA1_Channel1_IRQn, 0);

// 4. Start transfer

DMA1_Channel1->CCR |= DMA_CCR_EN;

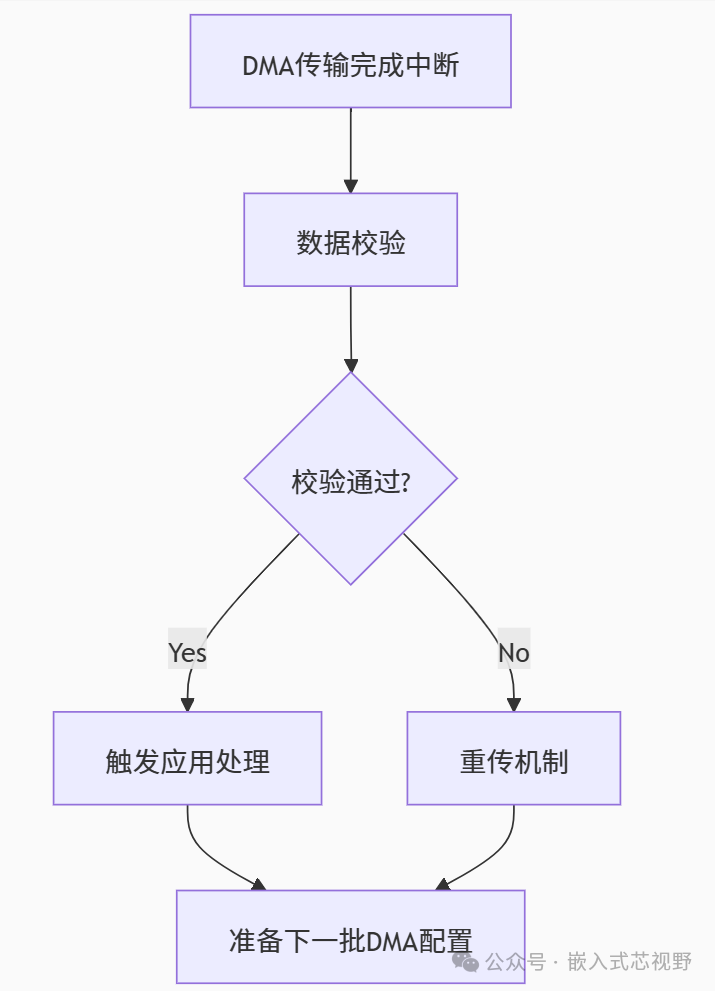

}Hybrid Mode Design:

Technical Selection Matrix

| Evaluation Dimension | Polling Driver | Interrupt-Driven | DMA-Driven |

|---|---|---|---|

| CPU Utilization | High (continuous utilization) | Medium (event-triggered) | Low (hardware autonomy) |

| Real-time Performance | Poor determinism | Microsecond-level response | Depends on transfer block size |

| Data Throughput | <1 Mbps | <10 Mbps | >100 Mbps |

| Implementation Complexity | ★☆☆☆☆ | ★★★☆☆ | ★★★★☆ |

| Power Consumption | Poor (continuous wake-up) | Good (fast sleep) | Excellent (deep sleep) |

| Typical Applications | GPIO state detection | UART message reception | SD card data storage |

Debugging and Optimization Techniques

-

Interrupt Storm Protection:

-

Add a watchdog timer

-

Implement interrupt frequency monitoring

volatile uint32_t isr_counter = 0;

void TIM2_IRQHandler(void) {

if(++isr_counter > MAX_ISR_RATE) {

SystemReset();

}

// ...other processing...

}2. DMA Transfer Diagnosis:

-

Use Memory Protection Unit (MPU) to detect out-of-bounds access

-

Configure DMA transfer complete/half transfer interrupts for double buffering

3.Power Optimization:

void EnterLowPowerMode(void) {

// Disable clock for unused peripherals

RCC->AHB1ENR &= ~(UNUSED_PERIPH_CLOCKS);

// Configure standby mode

PWR->CR |= PWR_CR_CWUF;

SCB->SCR |= SCB_SCR_SLEEPDEEP_Msk;

__WFI();

}Advanced Design Patterns

-

Producer-Consumer Model:

-

Interrupt/DMA as data producers

-

Application threads consume data via message queues

State Machine Driven:

typedef enum {

DRV_STATE_IDLE,

DRV_STATE_TX_PENDING,

DRV_STATE_RX_ACTIVE} DrvState_t;

void UartStateMachine(uint8_t event) {

static DrvState_t state = DRV_STATE_IDLE;

switch(state) {

case DRV_STATE_IDLE:

if(event == TX_REQUEST) {

StartDmaTransfer();

state = DRV_STATE_TX_PENDING;

}

break;

// ...other state transitions...

}

}3. Hardware Abstraction Layer (HAL) Design:

typedef struct {

void (*Init)(void);

bool (*Transmit)(uint8_t* data, uint16_t len);

bool (*Receive)(uint8_t* buffer, uint16_t len);

} DeviceDriver_t;

const DeviceDriver_t UartDriver = {

.Init = Uart_Initialize,

.Transmit = Uart_TransmitDma,

.Receive = Uart_ReceiveInterrupt};In actual project development, it is recommended to adopt a layered design strategy:

-

Encapsulate low-level hardware operations as atomic functions

-

Implement protocol parsing and state management in the middle layer

-

The application layer accesses driver services through standardized interfaces

By reasonably selecting driver modes and optimizing implementations, system performance can be improved by 3-5 times while reducing power consumption by over 60%. For critical task systems, a hybrid driver architecture is recommended: use DMA + interrupts for time-sensitive operations and periodic polling for state monitoring, achieving the best balance between performance and reliability.

Follow me for more technical insights.