This article is compiled by Semiconductor Industry Insight (ID: ICVIEW) from semiengineering.As design complexity increases, manual design methods struggle to minimize wire lengths.

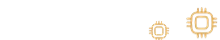

This article is compiled by Semiconductor Industry Insight (ID: ICVIEW) from semiengineering.As design complexity increases, manual design methods struggle to minimize wire lengths. In System on Chip (SoC) design, wire length refers to the total physical distance of interconnections within the Network on Chip (NoC). It is a critical parameter affecting performance, power consumption, and manufacturing costs. Today’s SoCs consist of numerous IP blocks interconnected by multiple complex NoCs, requiring effective management of wire lengths. In advanced deep submicron processes where interconnects dominate, excessive wire lengths can increase latency, power consumption, and complicate layout. Arteris’ FlexGen intelligent NoC IP is designed to address this challenge by automating NoC generation to minimize wire lengths while maintaining strict performance targets.As the complexity of SoCs increases, manual design methods applied to certain NoC components struggle to optimize wire lengths. For example, the total bus length of an automotive ADAS chip design developed manually by experts is 313,000 mm. Using FlexGen, which is not constrained by performance specifications, this number drops dramatically to 116,000 mm. When applying performance targets such as bandwidth and latency requirements, FlexGen achieves 280,800 mm. These results highlight FlexGen’s ability to revolutionize NoC design, providing measurable advantages over traditional methods and overall optimizing SoC design.

In System on Chip (SoC) design, wire length refers to the total physical distance of interconnections within the Network on Chip (NoC). It is a critical parameter affecting performance, power consumption, and manufacturing costs. Today’s SoCs consist of numerous IP blocks interconnected by multiple complex NoCs, requiring effective management of wire lengths. In advanced deep submicron processes where interconnects dominate, excessive wire lengths can increase latency, power consumption, and complicate layout. Arteris’ FlexGen intelligent NoC IP is designed to address this challenge by automating NoC generation to minimize wire lengths while maintaining strict performance targets.As the complexity of SoCs increases, manual design methods applied to certain NoC components struggle to optimize wire lengths. For example, the total bus length of an automotive ADAS chip design developed manually by experts is 313,000 mm. Using FlexGen, which is not constrained by performance specifications, this number drops dramatically to 116,000 mm. When applying performance targets such as bandwidth and latency requirements, FlexGen achieves 280,800 mm. These results highlight FlexGen’s ability to revolutionize NoC design, providing measurable advantages over traditional methods and overall optimizing SoC design. Utilizing FlexGen, intelligent NoC IP achieves wire length optimization. Source: Arteris

Utilizing FlexGen, intelligent NoC IP achieves wire length optimization. Source: Arteris Wire length optimizationWire length directly impacts design metrics, especially during the design process, where interconnects are more critical than gate circuits in terms of power and latency budgets. In SSD controller design, migrating from FlexNoC 5 to FlexGen can reduce wire length by 25%, improving power efficiency and accelerating signal transmission speed. In AI chip design, FlexGen achieves a 46% reduction in wire length, a 13% reduction in total chip area, and a 10% improvement in latency. While all use cases may vary due to set parameters, typical results are expected to save about 30% in wire length. These improvements stem from path optimization in the NoC request and response network (used as a data network). These benefits also include managing control networks for services and observability, ensuring effective communication across IP blocks.FlexGen leverages advanced automation techniques to explore NoC topologies (such as tree and mesh configurations) at speeds far exceeding manual methods. The NoC for the SSD controller requires 33 hours, including manual topology editing and automatic pipeline insertion, while FlexGen’s automation completes the task in 5.5 hours, with a 25% reduction in wire length. This efficiency arises from its ability to navigate blank areas between IP blocks while avoiding congestion. These areas are prohibited for routing to prevent metal shorts within IP blocks, ensuring optimized paths from slot positions to targets according to connection diagrams and performance specifications. Across different applications, FlexGen consistently reduces wire lengths by an average of 30%, enhancing energy efficiency, saving area, and accelerating signal transmission speed.

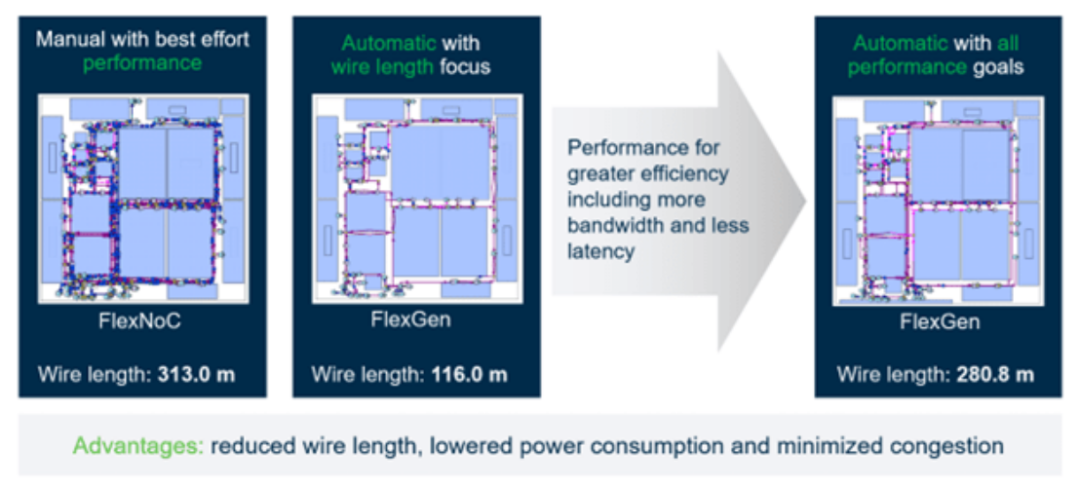

Wire length optimizationWire length directly impacts design metrics, especially during the design process, where interconnects are more critical than gate circuits in terms of power and latency budgets. In SSD controller design, migrating from FlexNoC 5 to FlexGen can reduce wire length by 25%, improving power efficiency and accelerating signal transmission speed. In AI chip design, FlexGen achieves a 46% reduction in wire length, a 13% reduction in total chip area, and a 10% improvement in latency. While all use cases may vary due to set parameters, typical results are expected to save about 30% in wire length. These improvements stem from path optimization in the NoC request and response network (used as a data network). These benefits also include managing control networks for services and observability, ensuring effective communication across IP blocks.FlexGen leverages advanced automation techniques to explore NoC topologies (such as tree and mesh configurations) at speeds far exceeding manual methods. The NoC for the SSD controller requires 33 hours, including manual topology editing and automatic pipeline insertion, while FlexGen’s automation completes the task in 5.5 hours, with a 25% reduction in wire length. This efficiency arises from its ability to navigate blank areas between IP blocks while avoiding congestion. These areas are prohibited for routing to prevent metal shorts within IP blocks, ensuring optimized paths from slot positions to targets according to connection diagrams and performance specifications. Across different applications, FlexGen consistently reduces wire lengths by an average of 30%, enhancing energy efficiency, saving area, and accelerating signal transmission speed. Precision and flexibilityBy dynamically adapting to various bit widths, FlexGen eliminates strict design constraints, making it easier to optimize NoC layouts, such as an 8-bit I/O linked to a 2048-bit data pipeline for high bandwidth memory (HBM). Unlike strict solutions that require uniform widths, FlexGen supports diverse connections within a single NoC. Timing convergence’s repeatable output is within 4%, allowing iterative refinement, distinguishing FlexGen from less predictable alternatives.

Precision and flexibilityBy dynamically adapting to various bit widths, FlexGen eliminates strict design constraints, making it easier to optimize NoC layouts, such as an 8-bit I/O linked to a 2048-bit data pipeline for high bandwidth memory (HBM). Unlike strict solutions that require uniform widths, FlexGen supports diverse connections within a single NoC. Timing convergence’s repeatable output is within 4%, allowing iterative refinement, distinguishing FlexGen from less predictable alternatives. FlexGen, intelligent NoC IP enables customizable automation. Source: ArterisFlexGen’s flexibility allows engineers to define traffic classes, including bandwidth-sensitive, latency-sensitive, and best-effort. This ensures that wire lengths align with specific design goals. In mid-range ADAS chips, this approach reduces wire lengths by 35% and saves 9% in area compared to manual operations. An Arteris tool expert user from a leading semiconductor company reported a 15-20% reduction in wire lengths. The tool integrates floorplan data via TCL or LEF/DEF formats and outputs to physical synthesis, providing timing convergence estimates, FIFO buffers for storage, and repeater pipelines to meet latency targets.Built on Arteris’ extensive NoC expertise, FlexGen offers production-ready solutions that significantly enhance NoC design efficiency and reduce wire lengths compared to traditional manual work. Semiconductor companies have shortened wire lengths, thereby reducing power consumption, latency, and manufacturing costs while accelerating design cycles. Whether optimizing network interface units for targets or optimizing complex SoC layouts, FlexGen sets a new benchmark for NoC design, solidifying Arteris’ leadership in interconnect IP technology.

FlexGen, intelligent NoC IP enables customizable automation. Source: ArterisFlexGen’s flexibility allows engineers to define traffic classes, including bandwidth-sensitive, latency-sensitive, and best-effort. This ensures that wire lengths align with specific design goals. In mid-range ADAS chips, this approach reduces wire lengths by 35% and saves 9% in area compared to manual operations. An Arteris tool expert user from a leading semiconductor company reported a 15-20% reduction in wire lengths. The tool integrates floorplan data via TCL or LEF/DEF formats and outputs to physical synthesis, providing timing convergence estimates, FIFO buffers for storage, and repeater pipelines to meet latency targets.Built on Arteris’ extensive NoC expertise, FlexGen offers production-ready solutions that significantly enhance NoC design efficiency and reduce wire lengths compared to traditional manual work. Semiconductor companies have shortened wire lengths, thereby reducing power consumption, latency, and manufacturing costs while accelerating design cycles. Whether optimizing network interface units for targets or optimizing complex SoC layouts, FlexGen sets a new benchmark for NoC design, solidifying Arteris’ leadership in interconnect IP technology. *Disclaimer: This article is original by the author. The content reflects the author’s personal views and does not represent the endorsement or support of Benno Electronic Materials for this viewpoint. If there are any objections, please contact Benno Electronic Materials, mobile WeChat same number: 17701718841.

*Disclaimer: This article is original by the author. The content reflects the author’s personal views and does not represent the endorsement or support of Benno Electronic Materials for this viewpoint. If there are any objections, please contact Benno Electronic Materials, mobile WeChat same number: 17701718841.