After two years of development, the AXIOM board has finally been launched. Initially, AXIOM was supported by seven different enterprises from Europe, including three research institutions/universities: the University of Siena, the Barcelona Supercomputing Center, and Fourth, along with four tech companies: SECo, Vimar, Evidence, and Herta Security.

The AXIOM board is the first to combine three different product lines: Arduino, ARM processors, and FPGA. In the design of AXIOM, the best components were chosen to achieve maximum real-time hardware acceleration with minimal resource and energy consumption. In other words, the AXIOM board successfully integrates high-performance computing, embedded computing, and cyber-physical system fusion. It is also an ideal platform for analyzing large amounts of data in a short time, such as machine learning, neural networks, server clusters, and Bitcoin mining.

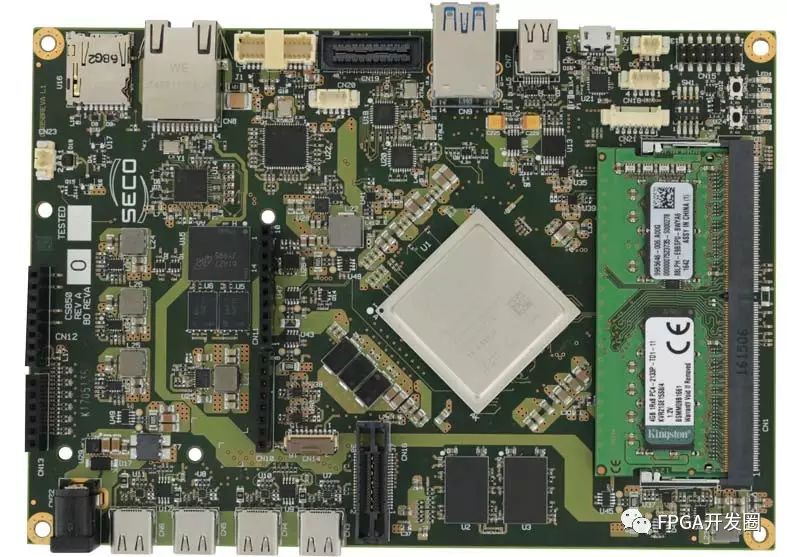

AXIOM Board Based on Xilinx Zynq UltraScale+ MPSoC Last month, the European AXIOM project team produced their first board, which is completely based on the Xilinx Zynq UltraScale+ ZU9EG MPSoC. The AXIOM project is equipped with highly sensitive, scalable, and fast I/O modules designed to address the latest hardware and software architecture issues in cyber-physical systems (CPS).

Figure 1: AXIOM Board Based on Xilinx Zynq UltraScale+ MPSoC (Front)

As shown in Figure 1, the pin layout of this board is identical to that of the Arduino Uno, allowing Arduino Uno compatible expansion boards to be installed on it. The AXIOM board adopts a pin allocation method similar to Arduino Uno, providing users with a more familiar operating method when constraining and configuring FPGA I/O pins.

Figure 2: AXIOM Engineering Board Based on Xilinx Zynq UltraScale+ MPSoC (Back)

In addition, the AXIOM board has the following features: 1) Strong boot compatibility, including eMMC, MicroSD, JTAG; 2) Heterogeneous 64-bit ARM FPGA processor: Xilinx Zynq UltraScale+ ZU9EG MPSoC; 3) 64-bit Quad-core A53 @ 1.2GHz; 4) 32-bit Dual-core R5 @ 500MHz; 5) DDR4 @ 2400MT/s; 6) Mali-400 GPU @ 600MHz; 7) 600K system logic units; 8) 32GB of swappable SO-DIMM RAM for processing systems; 1GB solid-state RAM for programmable logic units; 9) 12GTH wireless transceiver @ 12.5Gbps; 10) Easier designability (using Arduino Uno pin allocation method).

Conclusion: In today’s era of exploding data volume, analyzing massive data in a short time requires not only highly efficient software programs but also the need for high speed and performance. However, even if these conditions are met, the resulting machine can be complex to operate. AXIOM perfectly combines high-performance processing, ease of use (embedded, similar to Arduino), and hardware acceleration, successfully addressing this demand. In AXIOM, FPGA plays a crucial role. The Xilinx Zynq SoC series integrates single/dual-core ARM processors and hardware programmable units (FPGA), making Zynq the inevitable choice for implementing the AXIOM project.

Matrix Voice: A low-cost voice recognition platform with an embedded FPGA hardware accelerator

All Programmable SoC enters the manufacturing industry

Advantages of zero intermediate frequency architecture in radio design

Kickstarter crowdfunding: Dexter, a five-axis automated robotic arm based on MicroZed

In-depth analysis of ARM’s latest DynamIQ multi-core microarchitecture

How to convert ADC code to voltage (Part 1)

About high-impedance state and OOC (out of context) synthesis methods

Avnet UltraZed-EG SOM and expansion board introduction

reVISION makes its stunning debut, Xilinx simplifies vision-guided machine learning!

Exploring different SAR ADC analog input architectures

Optimizing embedded vision development on Xilinx devices with INT8

Nine often overlooked ADC technical specifications

[HLS Video Tutorial 17] FOR Loop Optimization – Data Flow

[Video] reVISION: Paving the way for vision-guided machine learning applications

Facing the 100Gbe challenge: BittWare StreamSleuth combats 100Gbps with FPGA hardware acceleration

A comprehensive guide to the Xilinx reVISION stack