CMake Practical Guide (Part One)

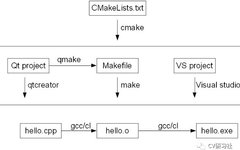

Click the blue text above to follow us Introduction Previously, we introduced the use of Autotools; today we will look at how to use CMake. CMake is a project build tool, similar to Autotools. It can be simply understood as a tool that helps us generate Makefiles for easier compilation. Usage Example (1) Create main.c, … Read more