The development of computer technology is extremely rapid. Thirty years ago, a small machine the size of a room had computing power that is still inferior to the CPU in today’s smartphones. Surprisingly, there is a technology from 38 years ago that is still widely used in computers today, and the number of its controllers in computers has doubled in the past five years. This technology is the I2C (Inter-Integrated Circuit, IIC) bus.

While some newcomers are still trying to understand the difference between I2C and another similar bus in computers, SMBus, a new bus I3C that replaces I2C has already appeared on the horizon. Those who track the latest technologies may have seen this name in Intel’s roadmap and DDR5 memory specifications. Now it is time to clarify the differences between I2C and SMBus and prepare for the arrival of I3C.

I2C vs SMBus?

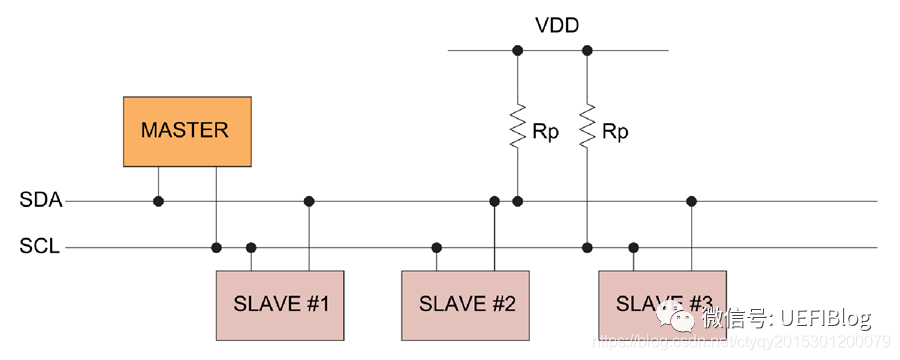

I2C (Inter-Integrated Circuit, IIC) was originally proposed by Philips Semiconductors (later merged into NXP) in 1982, primarily to provide a simple and low-cost serial bus for communication between MCUs and TV components. Initially, it was designed for one Master (with multiple Masters possible) to communicate with up to 127 Slaves over a bus consisting of two lines (SDA, SCL).

This allows the MCU to communicate with all peripheral devices happily using only two lines instead of needing to communicate separately with each device. These two lines are the data line (SDA) and the clock line (SCL). This greatly reduces the number of chip pins, facilitates motherboard wiring, and saves overall costs. Good design has gradually led to its widespread use. Over the years, I2C has undergone three version upgrades in terms of power saving and speed, increasing from 10KHz to a maximum of 5MHz. In the computer field, most low-speed devices communicate via I2C: most sensor data reading interfaces are I2C; the interface for clock chip CK404 is I2C; the reading interface for memory SPD information is I2C; some controller interfaces are I2C, and so on. With the increase in speed, some medium-speed devices also use I2C: common examples include laptop touchpads and touch panels, although the interface is HS I2C.

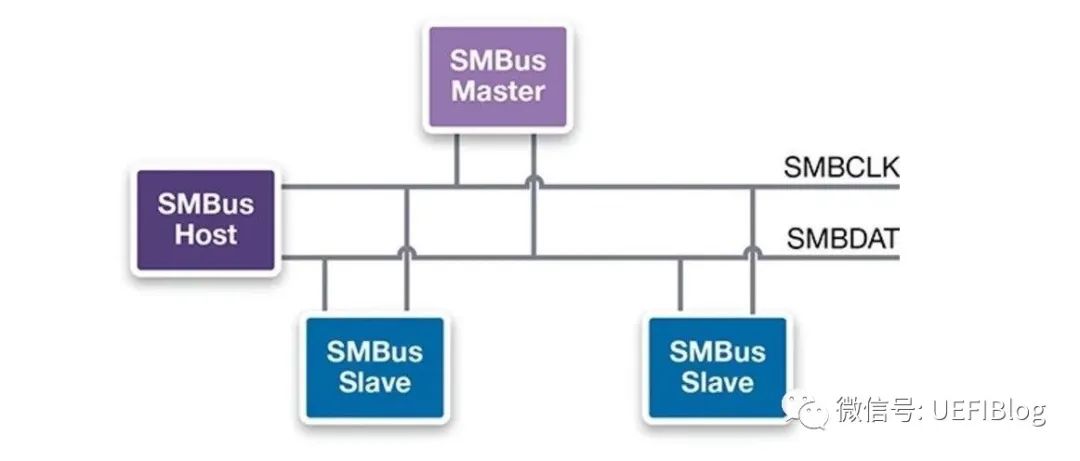

A similar bus that is often confused in computers is SMBus, which was released by Intel in 1995, initially used for communication with smart batteries, and has also undergone three enhancements, maturing around 2000 with little change since. SMBus is derived from I2C and can be considered a subset of I2C. In most cases, it also consists of one Master (with multiple Masters possible) and numerous Slaves communicating over two lines (SMBDAT and SMBCLK):

Under general applications, there is not much difference between I2C and SMBus; in fact, in most cases, they can be used interchangeably. What is more confusing is that both can appear in some designs, which leaves some students puzzled about the differences between the two. What is the point of reinventing the wheel with I2C?

The answer lies in the fact that I2C emphasizes speed, while SMBus emphasizes reliability and cost. I2C starts at 10KHz (theoretically it can be lower than 0) and goes up to 5MHz; while SMBus starts at a minimum of 10KHz and goes up to 100KHz. This means that between 10KHz and 100KHz, the two are interchangeable, excluding medium-speed and high-speed devices. I2C does not require Slaves to acknowledge address requests (ACK), while SMBus mandates ACK. Correspondingly, SMBus has stricter requirements for NACK than I2C. This is because SMBus is aimed at many removable devices in computers, and it is essential to confirm whether the device exists to avoid erroneous operations. SMBus also incorporates a watchdog function; after SMBCLK is pulled low, it must not exceed 35ms (this is the origin of the minimum frequency of 10KHz), or the Slave should reset. I2C does not have this restriction. This allows SMBus to avoid complex error recovery circuits. SMBus also provides a separate SMBSUS for Slaves to alert Masters.

What are the drawbacks of I2C?

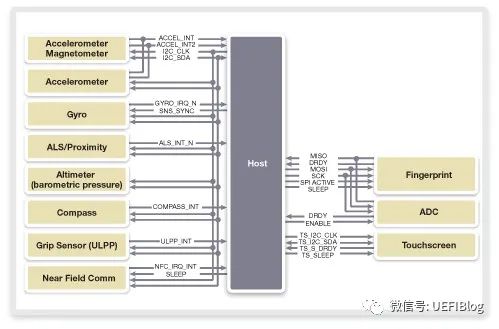

The design of I2C with its two lines is quite simple and efficient, allowing MCUs, PCHs, or CPUs to communicate through just two pins, saving costs and simplifying design. However, all communication is initiated by the Master, and the Slave merely responds passively, which can cause significant issues. This is acceptable for output devices, but for input devices, the CPU does not know if there is data and has to periodically pull the I2C bus to check for input, which contradicts the original intent of modern computer system design. As I2C becomes more widely used, more devices have added additional sideband lines to compensate for its shortcomings, with the two most important lines being the interrupt line INT and some RESET lines, as shown in the classic design below:

Classic I2C Design

In the diagram, the slow I2C devices on the left share an I2C bus, but each device has its own INT connected to the Host to notify the Host when something happens, instead of having the Host constantly polling. This allows the Host to enter a power-saving state when idle, making it more efficient. The high-speed devices on the right even have their own high-speed I2C bus. Thus, the ideal simple design is increasingly fragmented in reality, often with more INT lines than I2C lines. Coupled with the demand for further speed increases, the industry has called for a new solution. Hence, I3C is born.

I3C Has Arrived

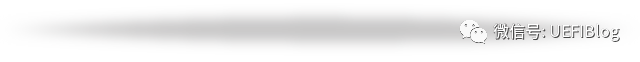

The MIPI Alliance has released the I3C standard [1] (Basic download available). I3C (Improved Inter Integrated Circuit), also known as SenseWire, is designed to meet the needs of sensors in numerous IoT devices. It brings numerous improvements, including the commonly mentioned speed increase to 12.5MHz:

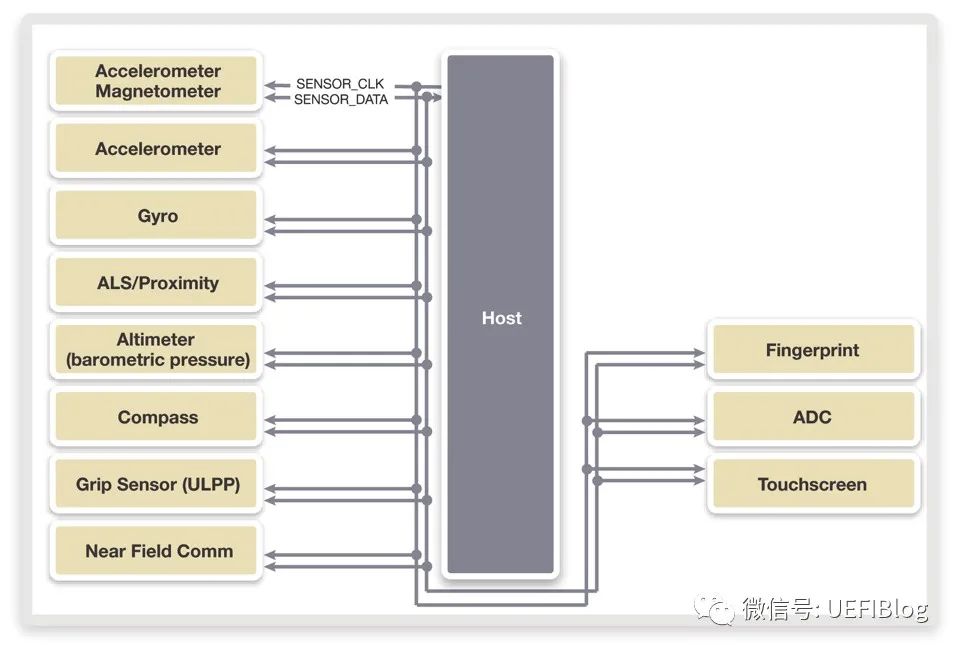

More importantly, it embeds soft interrupts into the protocol. Thus, there is no need for separate INT lines:

I3C Design

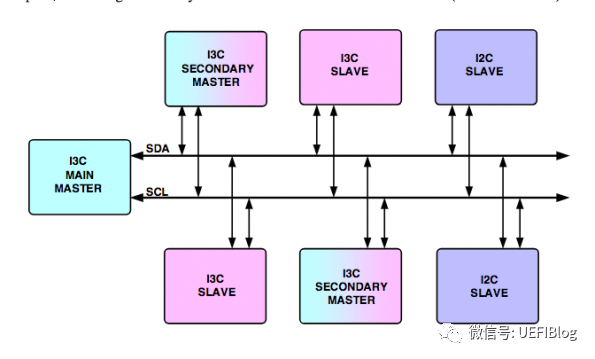

Numerous sideband lines are eliminated, and high-speed I2C is no longer necessary, achieving true speed and simplicity. It is also backward compatible with I2C, so older devices can still be used. A mixed system can be illustrated as follows:

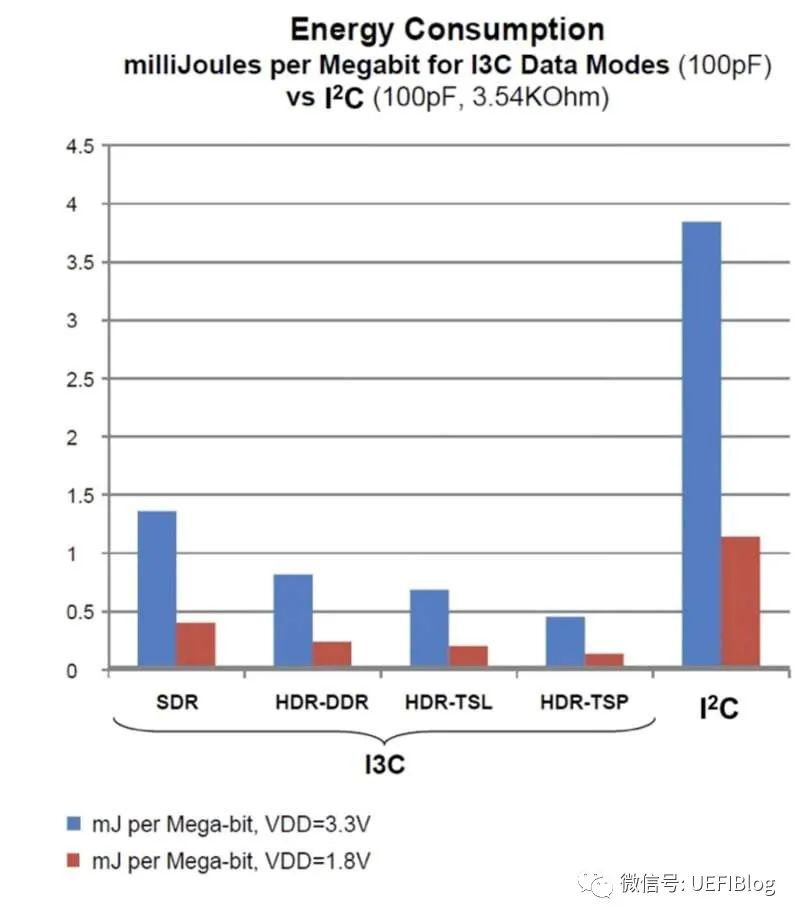

It also saves power consumption:

I3C has many other features: to simplify design, it proposed the I3C Hub; referencing the DDR memory concept, it introduced DDR double data transmission; supports power-saving modes; in-bound CRC checks; and allows direct communication between Slave and Slave.

Conclusion

Once, a student referred to I2C as “I(ai),2(er),C(ci)” and was ridiculed for it. The mocker arrogantly claimed, “It should be called I-square-C! This ‘2’ refers to ‘squared’!” Some even insisted on saying “I-squared-C” to show their technical prowess and knowledge. In reality, I hear American colleagues refer to it as “I-squared-C” and “I-two-C” about half the time, so the Chinese pronunciation “I(ai),2(er),C(ci)” is not unreasonable. As for I3C, I wonder how the proud students will refer to it in Chinese. Will it be called “I-cubed-C”? Perhaps it can be referred to as “I, 3, C” like in English.

References

[1]: MIPI I3C: https://www.mipi.org/specifications/i3c-sensor-specification