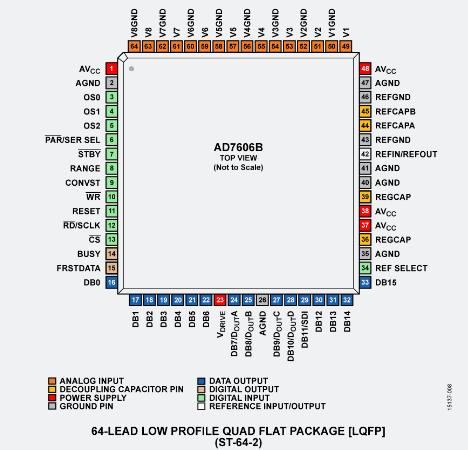

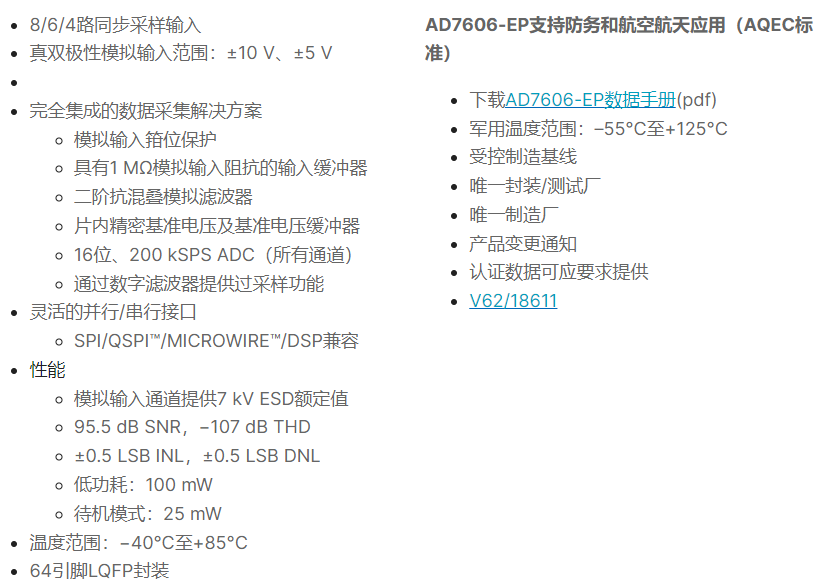

The AD7606/AD7606-6/AD7606-4 are 16-bit, 8/6/4 channel synchronous sampling Analog-to-Digital Conversion (ADC) systems. Each device includes built-in analog input clamping protection, second-order anti-aliasing filters, sample-and-hold amplifiers, 16-bit charge redistribution successive approximation ADCs, flexible digital filters, a 2.5 V reference voltage source, reference voltage buffering, and high-speed serial and parallel interfaces.

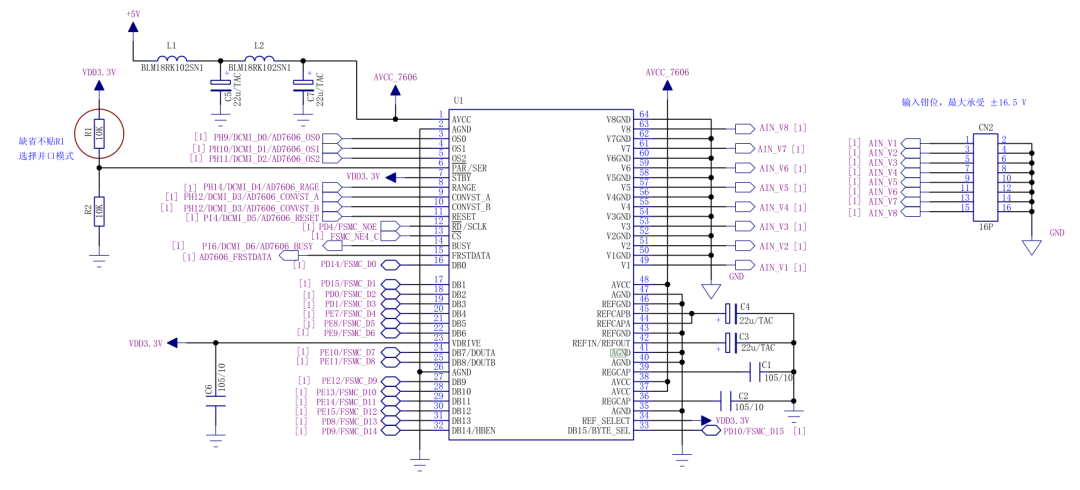

The AD7606/AD7606-6/AD7606-4 operates on a single 5 V power supply and can handle true bipolar input signals of ±10 V and ±5 V, while all channels can sample at a throughput rate of up to 200 kSPS. The input clamping protection circuit can withstand voltages up to ±16.5 V. Regardless of the sampling frequency, the analog input impedance of the AD7606 is 1 MΩ. It operates on a single power supply with on-chip filtering and high input impedance, eliminating the need for external operational amplifiers and bipolar power supplies. The 3 dB cutoff frequency of the anti-aliasing filter for the AD7606/AD7606-6/AD7606-4 is 22 kHz; when the sampling rate is 200 kSPS, it has a 40 dB anti-aliasing suppression characteristic. The flexible digital filter is pin-driven and can improve the signal-to-noise ratio (SNR) while reducing the 3 dB bandwidth.

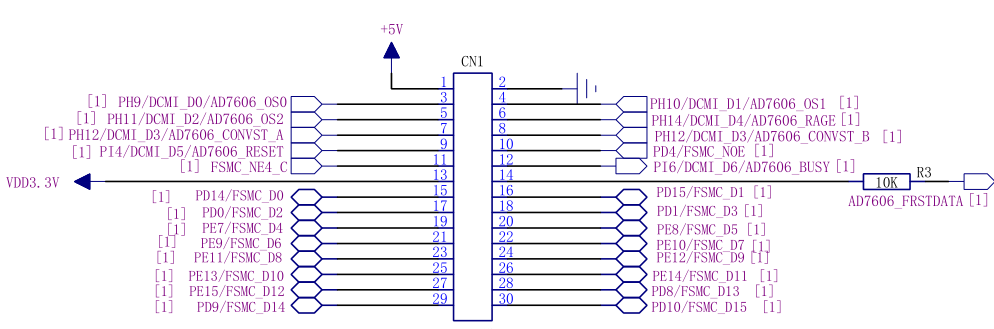

Schematic and Modules (As long as there are ready-made modules, there is still a lot of information):

Files shared via cloud storage:AD7606 Learning Materials.zip (Contents include: chip manual, schematic, program examples)

Link: https://pan.baidu.com/s/1huxgUchItTaLGTLBmVMvqg?pwd=gffk

Extraction Code: gffk

(Follow the official account for more: Learning hardware and software materials, experience sharing, software sharing, growth experiences)